durst

**AF 2000** Service manual

2.1

### Notice

This service manual has been edited in June 1992; the first unit name ELITE 2000 has been re-named in AF 2000.

This is the revised manual version 2.1 edited in May 1999 (updated circuit diagrams, corrected errors)

Utmost care was taken to ensure a flawless manual; we are, however, most grateful for all suggestions for improvement or correction.

For your suggestions please use the enclosed reply letter.

The service manual order code number is: **SM00550**

# **REPLY LETTER**

We'd like to receive your comments on this repair manual. Please answer the questions and return this form to: Durst Phototechnik AG, att. service department. Service manual for unit: 3. Version ☐ 1. Version 2. Version \_\_\_\_ Version Have you found any mistakes? Which? Did this manual help you to find an error cause? What was the mistake? What was the solution? Have you suggestions concerning the completion of the manual? Which topics should be added?

#### SUMMARY

- 1.1 General descriptions

- 2.2 Solid state devices

- 2.4 Factor potentiometer calibration

- 3.2 Testprogram

- 3.3 Continuous testprogram

- 3.B Flowcharts: processor keyboard display PCB

- 3.C Flowcharts: power supply

- 4.1 Processor PCB

- 5.5 Interface PCB

- 7.1 Elite 2000 TIM: lamp relay failure

- 7.2 Elite 2000 TIM: timer failure

- C.O Elite 2000 MOT: head movement failure

- D.1 Motor control 24 volts PCB: functional description

### DIAGRAMS

| - | Wiring diagram Head motor             | AM30401   |

|---|---------------------------------------|-----------|

| - | Wiring diagram Elite 2000 + AF module | MA60123   |

| - | Power control interface PCB           | MA60201   |

| - | Processor-keyboard-display PCB        | MA60302   |

| - | Motor control 24 V                    | MA83305   |

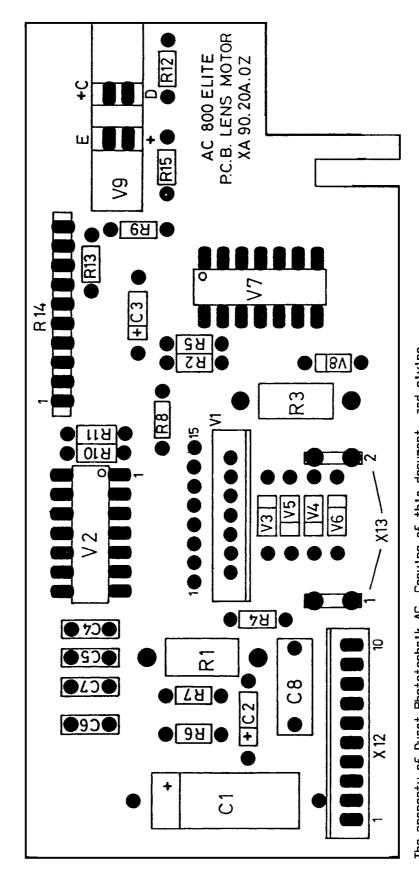

| - | Lens motor PCB                        | XA90201   |

| - | Soldering plane layout lens motor PCB | (XA9020A) |

#### 1.1 GENERAL DESCRIPTIONS

DURST ELITE 2000 - is a microprocessor-controlled autofocus System for Durst M 805 and L 1200 enlarger models

## Technical data

Lens carrier adjustment speed: fast = approx. 6.5 mm/sec.

slow = approx. 0.5 mm/sec.

Programmable lens focal lengths: from 35 up to 250 mm

Resolution of positioning device: 0.01 mm

Repeatability of lens setting:  $\pm$  0.02 mm

Environmental conditions: 30 - 80 % relative humidity

18 - 30 degrees centigrade

Lens Channels: 10 (0 - 9)

Positive variator range: + 999 / - 99 mm

Negative variator range: + 99 / - 99

For M 805 ELITE

Exposure timer range: 0 - 99.9 100-999 sec.

Lens aperture range: F/STOP 2.8 - 45

This service manual can be used for following variants:

Elite 2000 TIM autofocus control with timer Elite 2000 autofocus control without timer

Elite 2000 MOT autofocus control with motorized head movement control

On principle, they are interchangeable with regard to the automatic focusing function.

The main difference between the control desks lies in the number of keys on the keyboard, position of Jumper S 1 on the power control board and soldering bridge "M 805" on the keyboard.

The "MOT" version boasts an additional transformer, a  $24\ V_{-}$  motor control board and an interface PCB.

For functional description of the motor control, see D.1. For troubleshooting aid, see C.0.2

#### 1. Elite 2000 TIM

Processor keyboard PCB:

- keys S 11, 12, 13 are not mounted

- soldering bridge closed

- S 1 is open

### 2. Elite 2000

Processor keyboard PCB:

- keys S 11, 12, 13 are not mounted

- soldering bridge open

- S 1 is open

### 3. Elite 2000 MOT

Processor keyboard PCB:

- keys S 11, 12, 13 are mounted

- soldering bridge open

- S 1 is closed

## Operational description

The system consists of the Elite 2000 Control desk and the AF module.

The AF module is identical for all variants.

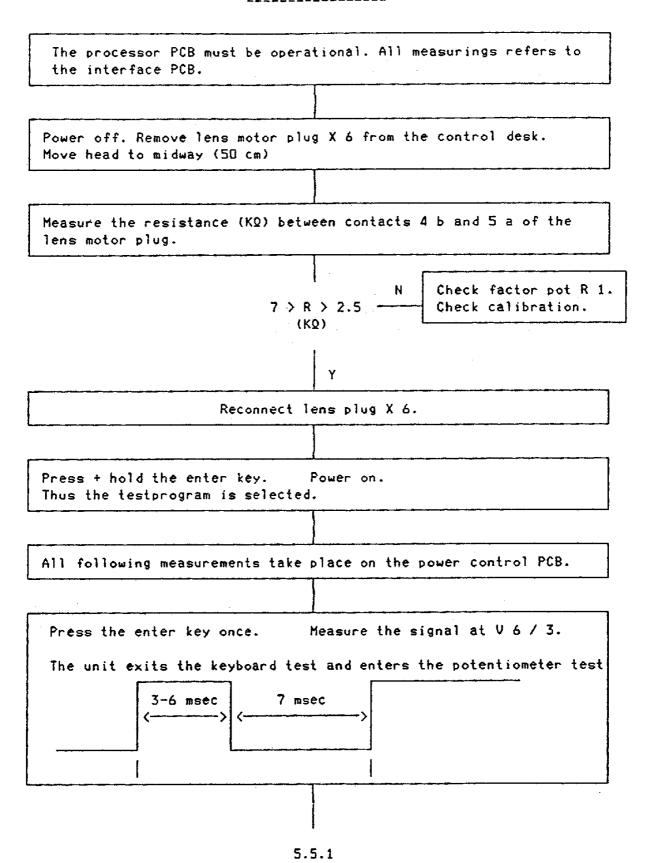

The system uses a potentiometer for feedback information about the colorheads vertical position.

The potentiometer resistance determines the duty cycle of monoflop V 6 on the power control interface PCB.

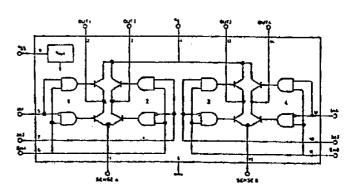

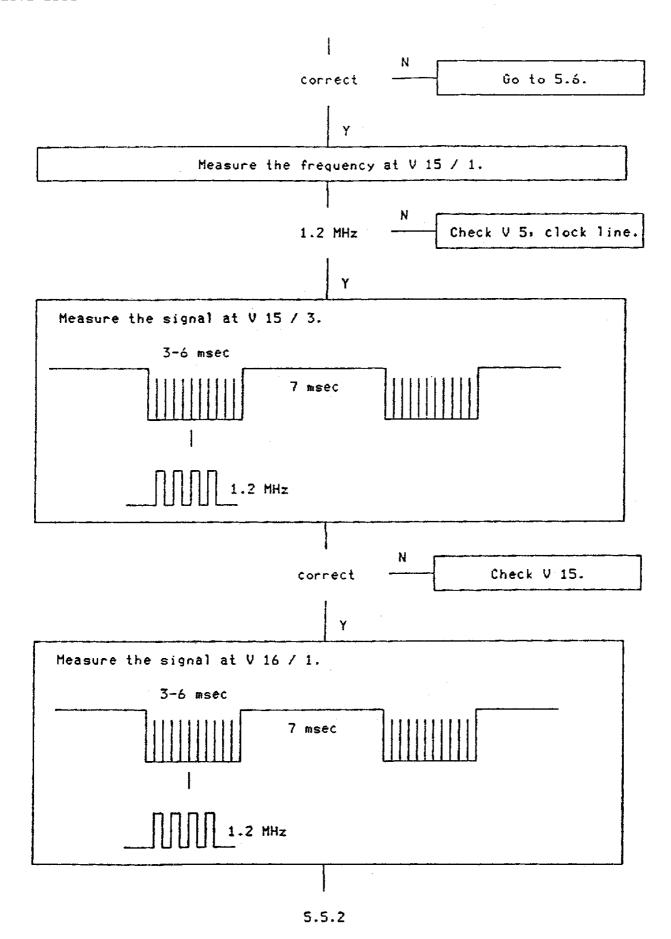

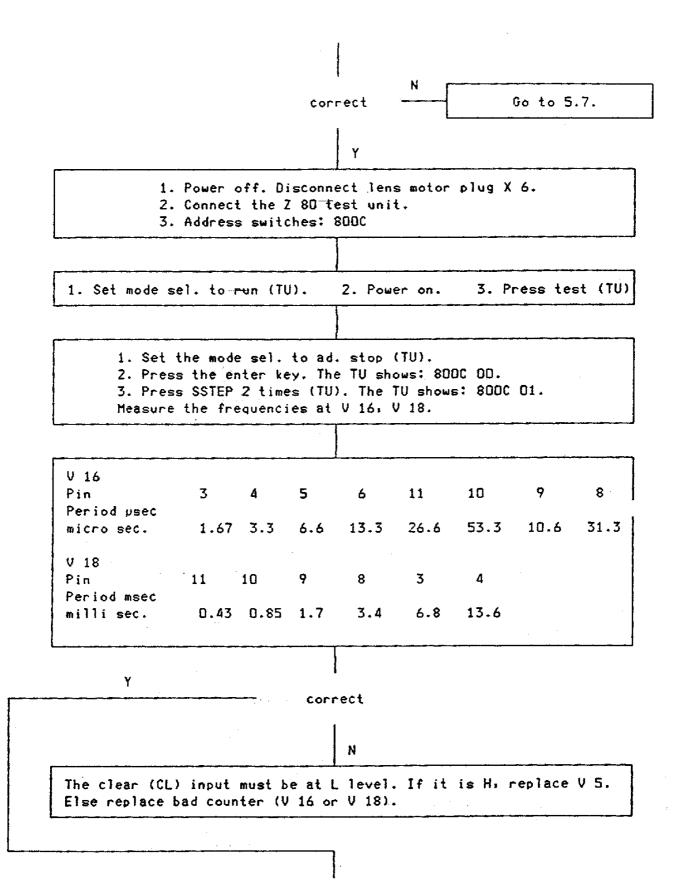

During this duty cycle (3-6 msec.) pulses of 1.2 MHz frequency are counted into binary counters V 16 and V 18. The duration of the duty cycle varies with the colorhead's height and thereby the number of pulses counted by V 16 and V 18.

Thus A/D conversion takes place.

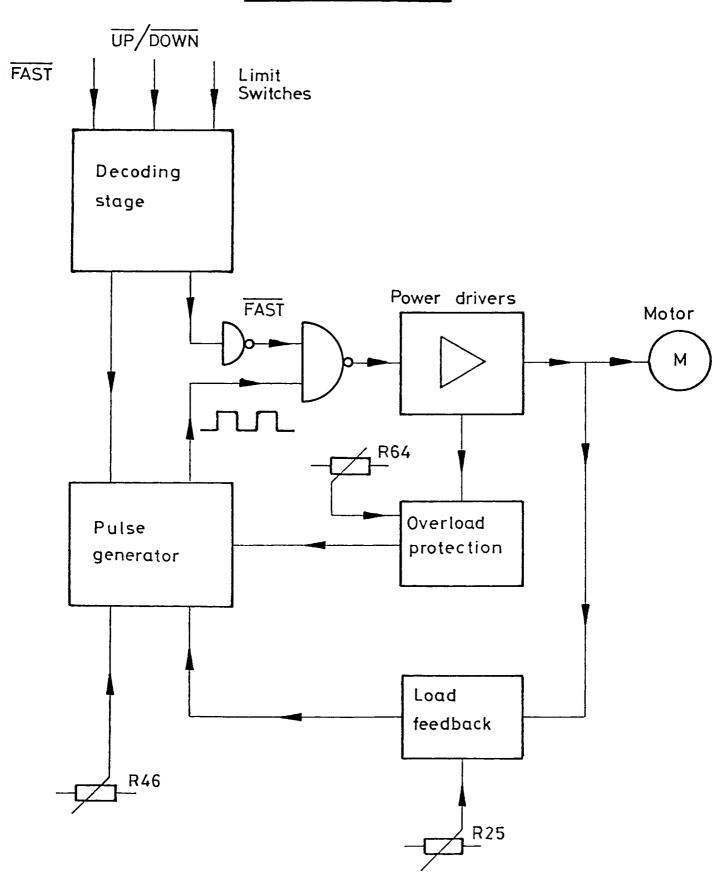

The microprocessor calculates the necessary lens displacement according to the programmed values. It activates the lens motor thru V 13, V 14 (interface PCb) and V  $_2$ , V  $_1$  on the lens motor PCB.

The lens motor is a 30 V DC motor. Thus a feedback becomes necessary, as to determine the real lens displacement.

An optical disk in connection with an optosensor (V 9) supplies the necessary pulses via V 2, V 7 to the power control PCB.

The microprocessor switches the pulses via the nand-gates V 15 to binary counters V 16 and V 18.

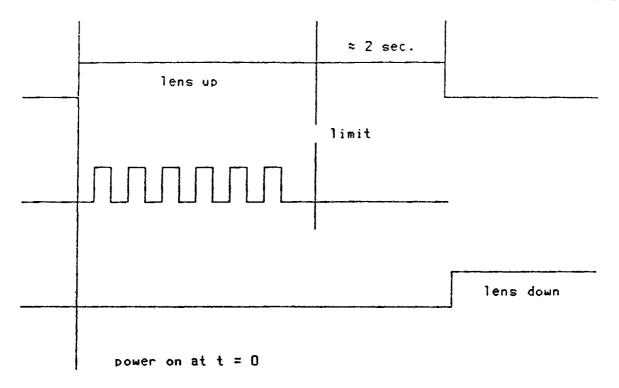

The lens reference position is determined after power on. The lens motor is activated and pulls the lens standard up to the stop position. Once the limit is reached, the optical disk stops supplying pulses. The microprocessor waits for approx. 2 seconds. If no pulses occur during this lapse, the position is taken for the upper lens limit position = reference position.

The microprocessor fetches the programming values, the potentiometer limit values from the register and polls counters V 16, V 18 (for actual colorhead position) to determine the necessary lens displacement.

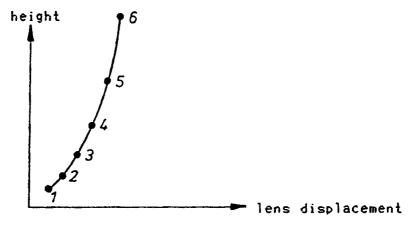

The programming values are determined during a programming session performed by the operator. The operator selects a cannel and focuses the lens manually at 5 or 6 different head positions.

The microprocessor stores the number of pulses which occur during each focussing operation. Once the session is over, all intermediate points are approximated by a curve.

### Note:

The head limit positions are stored in two registers inside the ram.

If the contents of the registers are lost, reprogramming becomes necessary (Refer to 2.4).

Otherwise the unit cannot be operated!!!

# Error messages:

Err. 7 - Error in the autofocus system

- Pulses missing

- Pulse sequence to slow

Err. 6 - Bad program values

# \* Z 80 + ENVIRONMENT

The microprocessor receives its instructions from eprom V 6.

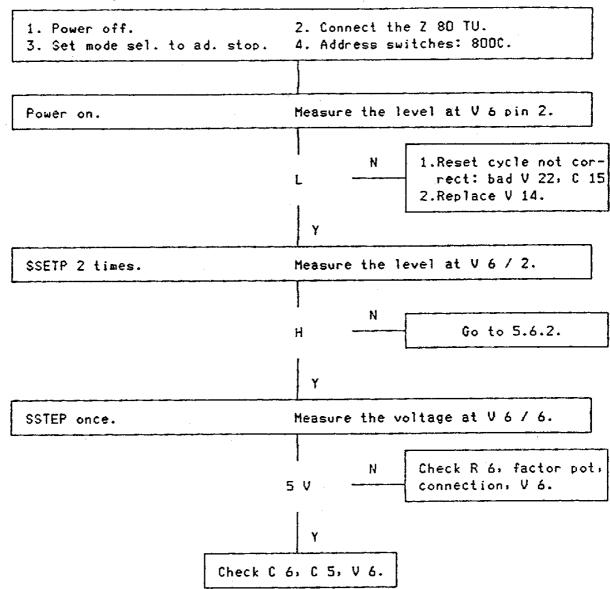

When power is applied to the system. V 22 on the power control interface PCB provides the 5 VDC supply voltage and a reset-signal. Once the reset signal goes to H, the processor starts operating.

The first operation is to fetch the first instruction contained in V 6. Therefore the read output goes to L, while V 5 is activated thru a MREQ signal.

V 5 decodes the inputs (A. B. C all L) and outputs YO goes L. Thereby eprom V 6 is enabled and delivers the data word contained in address 0000. The data word can be 1. 2 or 3 bytes long.

When a data word must be memorized: the WR output goes to L. The ram (V 7) is selected via address 4000 to 4FFF: and the data word present on the data inputs is memorized in the ram.

The data is retrieved when the processor puts out the correct address and the read output goes to L level.

The keyboard is selected via V 11. When pins 1 and 15 are at L level, this IC transfers the logic level at the "A" inputs to the "Y" outputs. The keyboard is a matrix-circuit.

The microprocessor selects one row of keys by supplying an appropriate address word.

When a key is pressed the corresponding line is pulled to 1 level.

V 11 transfers this logic state to the data bus: the microprocessor can "read" which key has been pressed.

V 12, V 28, V 29 form a multiplexing circuit to switch on one display or led-row at a time.

J 10 selects either keyboard, display or interface devices on the power control interface PCB.

# Address pages:

| 1/0 | address           | part                      |

|-----|-------------------|---------------------------|

| I   | 0000-3FF <b>F</b> | •prom                     |

| 1/0 | 4000-47FF         | ram                       |

| 0   | 0000              | interrupt reset           |

| 0   | 8000              | display multiplexer V 12  |

| 0   | 8004              | display high              |

| 0   | 8008              | display low               |

| I   | 8000              | any key                   |

| I   | 8006              | key-row 0 (\$ 10, 11, 12) |

| I   | 8005              | key-row 1 (\$ 6, 7, 8)    |

| I   | 8003              | key-row 2 (S 1: 2: 3)     |

# POWER CONTROL PCB

# Address pages:

| 1/0 | address | port |  |  |

|-----|---------|------|--|--|

| I   | 8010    | V 19 |  |  |

| I   | 8020    | V 17 |  |  |

| 0   | 800C    | V 14 |  |  |

| data                            | output str                                                    | ucture               | for V 14            |                       |                     |                       |                |

|---------------------------------|---------------------------------------------------------------|----------------------|---------------------|-----------------------|---------------------|-----------------------|----------------|

| DO                              | D 1                                                           | D 2                  | D 3                 | D 4                   | D 5                 | D 6                   | 7 0            |

| if 0:<br>count<br>lens<br>pulse | if 0:<br>reset coun-<br>ters and<br>trigger mo-<br>noflop V 6 | if 1:<br>relay<br>on | if 1:<br>lens<br>up | if 1:<br>lens<br>down | if 1:<br>head<br>up | if 1:<br>head<br>down | if 1:<br>rapid |

| if 1:<br>A/D con-<br>version    |                                                               |                      |                     |                       |                     |                       |                |

# 2.2 SOLID STATE DEVICES

| Microcomputer and IIL | CMQ\$       | DISCREIE           |

|-----------------------|-------------|--------------------|

| - Z 80 CPU            | - 4016      | - BC 237           |

| - 27128 eprom         | - 4070      | - BC 337           |

| - 5517 TC ram         | - 4098      | - BC 327           |

| - TIMER 555           |             | - IRF 532 (BUZ 20) |

| - 74 LS 138           | QEAMES      | - TIP 147          |

| - 74 LS 139           | - LM 339    |                    |

| - 74 LS 175           | - LM 324    | SEECIAL            |

| - 74 HCT 244          |             | - L 298            |

| - 74 LS 244           | SIABILIZERS |                    |

| - 74 LS 273           | - L 296     |                    |

| - 74 LS 374           | - 7812      |                    |

| - 74 LS 393           |             |                    |

#### General explanation of terms:

H: Logic high

L: Logic low

# Maximum input low:

This is the highest input voltage that the device will recognize as a low level. A higher voltage might be interpreted as high, or low. It is not defined.

## Minimum input high:

This is the minimum voltage required. So the device will recognize the level as being high. A lower voltage is not defined.

### Maximum output low:

The manufacturer guarantees that the device will not deliver a voltage lower than this if the output is at L level.

### Minimum output high:

The device will deliver a voltage which is not lower than this value, if the output is at H level.

# Z 80 CPU

The Z 80 central processing unit is 8 bit microprocessor which may run on 2.5 MHz to 8 MHz clocks.

Operation is possible with supply voltage 4.74 V ≤ VCC ≤ 5.25 V.

Operating temperature range is  $0^{\circ}$  to  $70^{\circ}$  C.

Maximum input low: 0.8 V

" high: 7 V

Minimum input low: - 0.7 VCC

" high: 2 VCC

Maximum output low: 0.4 V Minimum "high: 2.4 V

All outputs can either be high, low or high impedance.

The Z 80 CPU is capable of arithmethic, logic and 1/0 operations. The CPU accepts 2 interrupt input signals:

- NMI (non maskable interrupt)

- INT

The NMI has first priority.

The INT input has lower priority and its acknowledgement must be enabled thru an instruction in the software.

The NMI cannot be disabled thru software.

After detection of the NMI input signal (pin 17 goes L) the CPU jumps to 0066 (H).

The INT input is acknowledged only if the bus req input is not active.

# A 0 - A 15 ADDRESS BUS

The 16 bit address bus supplies the addresses for selecting I/O ports and memory locations in the rams / eproms.

Each I/O port is selected by an address combined with a read or write signal. Thus the CPU is enabled to read or write data from external devices like sensors, counters and activate motors.

## D O - D 7 DATA BUS

\_\_\_\_\_

The 8 data inputs / outputs are used for data exchanges with memory devices (ram, eproms) and I/O ports.

## M 1 MACHINE CYCLE ONE

\_\_\_\_\_

This output carries information:

If M 1 is active together with MREQ (both active L), it indicates that during the current cycle the opcode is fetched.

If M 1 is active together with the IORQ output, the CPU has acknowledged an interrupt signal.

### RESET (input, active low)

\_\_\_\_\_\_

The reset input initializes the CPU, clears all registers.

While the reset input is L. the address and data bus go to high impedance.

### WR

--

When the write output goes to L state, the CPU data bus holds valid data to be stored at the memory location or I/O port indicated on the address bus.

### Manufacturers:

- Zilog

- Mostek

- Toshiba

- SG\$

27128

The 27128 is an UV erasable electrically programmable memories with

16 KByte storage = 128 Kbits

Operating temperature range: 0° - 70 70°C

Power supply VCC:

5 V ± 0.25

Input L voltage:

min. - 0.1

max. .0.8 V

Input H voltage:

min. 2 V max. 5.7 V

Output L voltage:

max. 0.45 V

Output H voltage:

min. 2.4 U

Maximum active current:

125 mA

Maximum standby current: 30 mA

## **ERASURE**

Erasure occurs when the window is exposed to wavelengths shorter than 4000 A.

Sunlight and certain fluorescent lights can erase the eprom.

The opaque label should be left in place.

# DEVICE OPERATION

------

₹ead

The 27128 has two control inputs: OE and CE. Both must be active (L) to obtain iata at the outputs.

## STANDBY

\_\_\_\_\_

When the CE input is H, the 27128 goes to standby mode independent of the OE input.

The max. current consumption falls to less than 40 mA.

5517

The 5517 is a 2 KByte random access memory. Each byte contains 8 bits.

The 5517 has 2 control inputs: CE and OE.

Both must be active (L) to access the memory. When the CE input is H. the memory switches to standby mode and current consumption drops to 1 micro ampere.

| OPERATION | R/W | 0E | CE |

|-----------|-----|----|----|

| Read      | Н   | L  | L  |

| Write     | L   | Н  | L  |

| Standby   | X   | Х  | Н  |

The 5517 is pin compatible with the TMR2016P (Texax Instruments).

Fower supply voltage VCC: 4.5 to 5.5 V

Input High: 2.2 " 5.3 V

Input Low: - 0.3 " 0.8 V

Data retention voltage: 2 < VCC < 5.5

Manufacturer: Toshiba

NE 555: Timing circuit

is compatible with: MC 1455/1555 (Motorola)

SE 555

Uses an external resistor - capacitor network as timing controllers. Both monostable and astable operation are possible. The output timing is independent of the supply voltage.

### Monostable mode (see circuit diagram)

On the interface PCB the 555 is used as one-shot circuit with variable duty cycle. The trigger signal is provided by the CPU via V 14. When pin 2 is at H level, capacitor C 5 is short circuited by an internal transistor. Once the level at pin 2 drops below 1/3 VCC, the 555 is triggered.

The internal transistor is disabled.

Output pin 3 goes to H level. C 5 can charge up at an exponential rate thru R 6 and the factor potentiometer.

Once it reaches 2/3 of VCC, the circuit resets itself and pin 3 returns to L level.

| RATINGS                 | min. | wax.    |

|-------------------------|------|---------|

| Supply voltage (VCC)    | 4.5  | 18      |

| Output L                |      | 0.5     |

| Output H                | 3    |         |

| Highest trigger voltage |      | 1/3 VCC |

# Manufacturers:

- National

- Texas Instruments

- Fairchild

# 74LS138: Decoder / Multiplexer

### RATINGS:

Typical power dissipation: 32 mW

Supply voltage: 4.5 - 5.5 V

Operating air temperature: 0 - 70°C

High level input voltage: min.: 2 V

Low " " " max.: 0.8 V

High level output voltage: min.: 2.7 V

Low " " " max.: 0.4 V

Absolute max.-supply voltage: 7 V

input " 5.5 V

# TRUTH TABLE

| Inputs |     |             |         | Out | outs |    |    |    |    |

|--------|-----|-------------|---------|-----|------|----|----|----|----|

| Enable |     |             | Address |     |      |    |    |    |    |

| G1     | G2A | <b>G</b> 2B | CBA     | YO  | Y1   | Y2 | Y3 | Y4 | Y5 |

| X      | X   | H           | x x x   | Н   | Н    | н  | н  | н  | н  |

| L      | Х   | X           | XXX     | Н   | Н    | Н  | Н  | Н  | Н  |

| X      | н   | X           | XXX     | Н   | H    | Н  | Н  | H  | H, |

| Н      | L   | L           | LLL     | L   | Н    | Н  | Н  | H  | H  |

| H      | L   | L           | LLH     | Н   | L    | Н  | H  | Н  | Н  |

| Н      | L   | L           | LHL     | н   | H    | L  | H  | Н  | H  |

| Н      | L   | L           | LHH     | Н   | Н    | Н  | L  | Н  | Н  |

| Н      | L   | L           | HLL     | н   | H    | Н  | Н  | L. | Н  |

| Н      | L   | L           | нцн     | н   | Н    | H  | H  | Н  | L  |

|        |     |             |         |     |      |    |    |    |    |

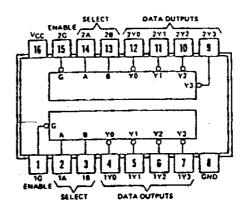

# 74LS139

1463137

This IC contains two fully independent 2 to 4 line decoders / multiplexers.

# Electrical characteristics

Typical power dissipation: 34 mW

| far. | ameter                             | Test conditions           |                                       |                      |      | L\$139       |      | Unit |

|------|------------------------------------|---------------------------|---------------------------------------|----------------------|------|--------------|------|------|

|      |                                    |                           |                                       |                      | min. | typ          | max. |      |

| VIH  | high level input<br>voltage        |                           |                                       |                      | 2    |              |      | U    |

| VIL  | low level input<br>voltage         |                           | · · · · · · · · · · · · · · · · · · · |                      |      |              | 0.8  | V    |

| VОН  | high level output<br>voltage       | VCC=min.<br>VIL=VIL max.  | VIH=2 V<br>IOH=-400 µA                |                      | 2.7  | 3.4          |      | U.   |

| VOL  | low level output<br>voltage        | VCC=min.<br>VIL=VIL max.  | VIH=2 V                               | IOL=4 mA<br>IOL=8 mA |      | 0.25<br>0.35 | 1    | v    |

| II   | Input current at max input voltage | VCC=ma×.                  | VI=7 V                                |                      |      |              | 0.1  | mΑ   |

| IIH  | High level input                   | VCC≃ma×.                  | VI≃2.7 V                              | :                    |      |              | 20   | μA   |

|      | Low level input<br>current         | VCC=max.                  | VI=0.4 V                              |                      |      |              | -0.4 | mΑ   |

| IOS  | Short circuit output current \$    | VCC=max.                  |                                       | LS139A               | -20  |              | -100 | mΑ   |

| IOS  | Supply current                     | VCC=max.<br>Outputs enabl | ed and open                           | LS139A               |      | 6.8          | 11   | mΑ   |

# LS139A (EACH DECODER/DEMULTIPLEXER)

#### FUNCTION TABLE

| Inputs |        |   |    | Outp | uts |    |

|--------|--------|---|----|------|-----|----|

| Enable | Select |   |    |      |     |    |

| . G    | В      | Α | YO | Y1   | Y2  | Y3 |

| Н      | Х      | Х | Н  | Н    | Н   | H  |

| L      | L      | L | L  | Н    | Н   | Н  |

| L      | L      | н | Н  | L    | Н   | н  |

| L      | H      | L | Н  | H    | L   | н  |

| L      | Н      | н | H  | Н    | Н   | L  |

H = high level, L = low level, X = irrelevant

74LS244: 2 x 4 buffers with tree-state outputs

The 2 fully indipendent, noninverting buffers have each:

- 1 enable input (L acitve)

- 4 inputs (L or H)

- 4 outputs (three-state)

# RATINGS:

Supply voltage: 4.75 - 5.25 V Temperature range: 0 - 70°C

High level input voltage: min. 2 V Low " " max. 0.8 V

High level output voltage: min. 2 V Low " " max. 0.55 V

# 74L\$175

Contains 4 D flip-flops.

Each FF is edge-triggered by the same clock signal.

The level at the "data" input is transferred to the output upon the rising edge of the clock signal.

The output remains at this level until new data is transferred with a clock signal or until the "MR" (master reset) input is activated.

## TRUTH TABLE

| OPERATING MODE | INPUTS |    |    | OUTPUTS |    |  |

|----------------|--------|----|----|---------|----|--|

|                | MR     | CP | DN | NO      | ŌΝ |  |

| Reset (clear)  | Ĺ      | Х  | x  | L       | Н  |  |

| Load "1"       | H      | †  | H  | H       | L  |  |

| Load "O"       | L      | Ť  | L  | L       | H  |  |

Note that each FF has 2 outputs, with complementary status.

# ELECTRICAL CHARACTERISTICS

| VOH: | Min. high | level outp  | ut voltage: |   | 2.5 |    |

|------|-----------|-------------|-------------|---|-----|----|

| VOL: | Max. low  | 11 11       | 41          |   | 0.5 |    |

| IN:  | " inpu    | t current ( | VIN = 7 V): |   | 1   | mΑ |

| IH:  | Max. high | level inpu  | t current:  |   | 0.1 | mΑ |

| TL:  | Max. low  | H H         | 11          | - | 2   | mΑ |

# 74LS273: Eight D flip-flops

### FUNCTION:

The level at the D input is transferred to the O output on the rising edge of the clock input.

When the clock is at either H or L, the D input has no influence on the Q output

The clear input resets all the Q outputs to L level.

### TRUTH TABLE

| Clear | Clock    | Di | Qi        |

|-------|----------|----|-----------|

| L     | X        | X  | L         |

| Н     | †        | Н  | Н         |

| H     | <b>†</b> | Ł  | L         |

| Н     | H        | X  | NO CHANGE |

### RATINGS:

| Supply voltage:<br>Temperature range: |       |         | 4.5 - 5.5 V<br>0 - 70°C  |

|---------------------------------------|-------|---------|--------------------------|

| High<br>Low                           |       | input:  | mîn. 2 V<br>max. 0.8 V   |

| High<br>Low                           | level | output: | min. 2.4 V<br>max. 0.4 V |

# 74LS393: $2 \times 4$ bit binary counters

The 73LS393 frequency dividers / counters contain 2 indipendent counters which can be cascaded. Each has a clear (active H) and a clock input.

The output changes on the negative-going edge of the clock input. A frequency at the clock input is divided by:

|    |    |    |    | if cas | if cascaded |     |     |  |  |

|----|----|----|----|--------|-------------|-----|-----|--|--|

| 2  | 4  | 8  | 16 | 32     | 64          | 128 | 256 |  |  |

| QA | QB | QC | QD | QA     | QB          | QC  | QD  |  |  |

# 74HCT244: CMOS non-inverting octal 3-state line driver

The pinout is identical with the 74LS244.

# TRUTH TABLE

G In OUTn

H X HighZ L L L L H H

# ELECTRICAL CHARACTERISTICS

| VIH | Min.   | high | level | input:  | 3.2 | V |

|-----|--------|------|-------|---------|-----|---|

| VIL | . Max. | low  | н     | 41      | 1   | V |

| VOH | Min.   | high | 44    | output: | 3.7 | V |

| VOL | Max.   | low  | 44    | 44      | 0.4 | V |

74L\$374: 8 D-latches

# ELECTRICAL CHARACTERISTICS

| parameter |                                                            | test conditions                                           | SN74LS |              |          | unit |

|-----------|------------------------------------------------------------|-----------------------------------------------------------|--------|--------------|----------|------|

|           |                                                            |                                                           | min.   | typ.         | max.     |      |

| VIH       | high level input V                                         |                                                           | 2      |              |          | V    |

| VIL       | low level input V                                          |                                                           | ,2     |              | 0.8      | v    |

| ион       | high level output V                                        | VCC=min. VIH=2V<br>VIL=VILmax. IOH=max.                   | 2.4    | 3.1          |          | υ    |

| VOL       | low level output V                                         | VCC=min. VIH=2V IOL=12mA<br>VIL=VILmax. IOH=max. IOL=24mA |        | 0.25<br>0.35 |          | v    |

| 10ZH      | off-state output<br>current, high level<br>voltage applied | VCC=max. VIH=2V<br>VD=2.7V                                |        |              | 20       | Αu   |

| ICC       | supply current                                             | VCC=max.<br>Output control at 4.5 V                       |        | 24<br>27     | 40<br>40 | mA   |

#### Description

The eight flip-flops of the LS374 are edge-triggered D-type flip-flops. On the positive transition of the clock, the Q outputs will be set to the logic states that were setup at the D inputs.

Due to Schmitt-trigger buffered inputs at the enable/clock lines noice rejection is typically 400 mV. A buffered output control input can be used to place the eight outputs in either a normal logic state (high or low logic levels) or a high-impedance state. In the high-impedance state the outputs neither load nor drive the bus lines significantly.

The output control does not affect the internal operation of the latches or flip-flops. That is, the old data can be retained or new data can be entered even while the outputs are off.

| OUTPUT<br>CONTROL | CLOCK            | D           | CUTPUT            |

|-------------------|------------------|-------------|-------------------|

| L L H             | †<br>†<br>L<br>X | H<br>L<br>X | H<br>L<br>QO<br>Z |

# 4016: bilateral switches

These C-MOS switches can transmit analor or digital signals.

Each package contains 4 switches.

The on/off state is controlled by a digital signal at the control inputs.

A H level turns the switch on, I L level turns it off.

Max. "ON" resistance at VDD = 10 V is  $600 \Omega$

4070B: quad ex-or gates

TRUTH TABLE

| A | В | 007 |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | Ð   |

ELECTRICAL CHARACTERISTICS: (for VDD = 10 V)

Output voltage: max. L level: 0.05 V min. H 9.95 V

Input voltage: max. L level: 3 V min. H " 7 V

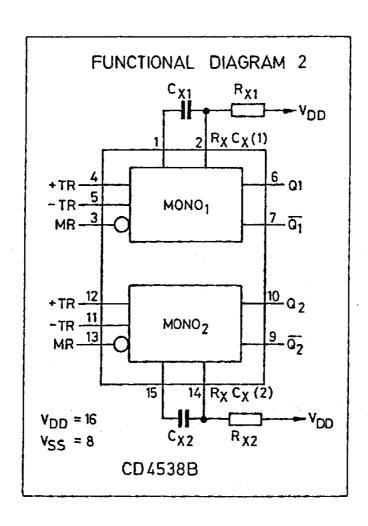

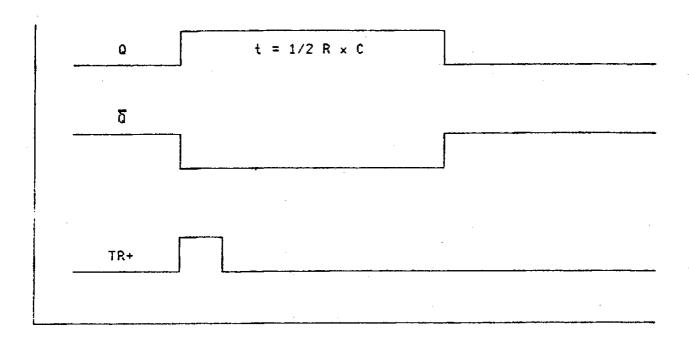

4098: dual monostable multivibrator (monoflop)

Provides one shot retriggerable operation.

If retriggering during the active period is not desired,  $\delta$  can be tied to TR- or 0 to TR+ depending it leading or trailing edge triggering is used.

The active period can be calculated as follows:  $1/2 R \times C$

### PIN DESCRIPTION

RX, CX

External resistor R and capacitor C determine the active period.

TR

TR+ and TR- start the monoflop.

TR+ is used if leading edge triggering is desired TR- " " trailing " " " "

MR

**ELITE 2000**

A low level at this input immediately resets the monoflop.

This output is H during the active period and returns to L after the period has finished.

This output is L during the active period and returns to H after the period has finished.

LM324: Quad operational amplifiers

Replacements: MC1741, MC3503, MC3403

### Features:

Short circuit protected output Max. supply voltage: 36 V 4 amplifiers per package ± 13 V output swing

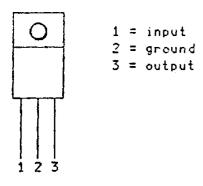

# 7805 / 7808 / 7812: Three terminal positive voltage regulators

7805 - 5 V regulator 7808 - 8 V "

7812 - 12 V "

Types with different current capability are available. Some can supply up to 2 A continuous output current.

The regulators are short circuit and heat protected.

#### CURRENT CAPABILITIS:

Type: max. continuous current:

The regulators do not require any external components for voltage regulation.

The fixed output voltage can vary from one to the other IC: following are typical dispensions:

7805 4.3 to 5.2 V 7808 7.7 " 8.3 V 7812 11.5 " 12.5 V

The regulator keeps this voltage pretty much constant over a wide range of load variations.

| Type | AV           | load variation | line variation |

|------|--------------|----------------|----------------|

| 7805 | 50 mV (max)  | 5 to 500 mA    | 7 - 30 V       |

| 7808 | 80 mV (max)  | 5 to 500 mA    | 10 - 30 V      |

| 7812 | 120 mV (max) | 5 to 500 mA    | 14 - 30 V      |

BC237B: silicon NPN small signal transistor

MAX. RATINGS

VCB0 50 V VCE0 45 V VBE 6 V IC 100 mA PTOT 0.3 W

ELECTRICAL CHARACTERISTICS

hFE  $200 - 500 \cdot (IC = 2 \text{ mA}, VCE = 5 \text{ V})$

Replacements: BC182, BC107

BC307: PNP silicon transistor

For ratings see 80237.

Replacements: BC161B, BC177

BC338: NPN silicon transistor

MAX. RATINGS

VCB0: 30 V VCE0: 25 V VEB0: 5 V IC: 0.8 A PTOT: 0.625 W

ELECTRICAL CHARACTERISTICS

hFE: 100 - 600 (IC 100 mA)

VCE (SAT): 0.7 V

Replacements: BC337, BC239

# BC327: PNP transistor

Max. collector-emitter voltage (VBE = 0): 50 V

Max. continuous collector current: 0.5 A

Max. base current: 0.1 A

hFE: 100 - 600

BC327 can be replace by BC297.

# THE IRF532: Power MOS field-effect transistor

Is a n-channel enhancement MOS transistor.

Replacements: BUZ 20, RFP12N10 (RCA)

### ELECTRICAL CHARACTERISTICS

Drain source breakdown voltage: 100 V

VGS Fhreshold: 2 - 4 V

ID (ON): 12 A

gfs: 5.5 Siemens (typ)

vds (ON): 0.18 Q

Max power diss.: 75 W

# TIP147: Epitaxial PNP power Darlington transistor

# ELECTRICAL CHARACTERISTICS - (MAX. RATINGS:)

VCEO: 100 V VEBO: 5 V ICM: 20 A IB: 0.5 A PTOT: 125 W

# OPERATING CHARACTERISTICS

VCE at IC = 30 mA: 100 V VBE at IC = 10 A, VCE = 4 V: 3 V hFE at IC = 10 A, VCE = 4 V: 500

Replacements: BDV64B

# L298: Dual full-bridge driver

### ABSOLUTE MAX. RATINGS

# VS Power supply: 50 V VSS Logic supply voltage: 7 V

IO Peak output current:

non repetive: DC:

2

3 A 2 A

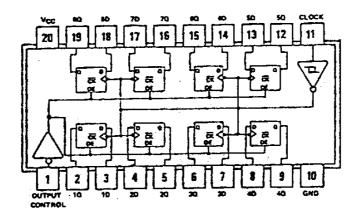

### BLOCK DIAGRAM

#### Manufacturers:

- SGS

- Unitrade

# L296: Switching regulator

#### RATINGS

| Ma×. | input voltage:   |     |    |    |   | 50  | ٧ |

|------|------------------|-----|----|----|---|-----|---|

| Max. | voltage at pins: | 1.  | 12 |    |   | 10  | V |

|      |                  | 6,  | 15 |    |   | 15  | V |

|      |                  | 4,  | 5, | 7, | 9 | 5.5 | V |

|      |                  | 10, | 6  |    |   | 7   | V |

If these limits are exceeded, the circuit will be damaged.

### **FUNCTION**

The circuit is internally over-load protected.

The capaciton at his 5 determines the cost ptace

The capacitor at pin 5 determines the soft start delay. The capacitor at pin 13 determines the reset delay.

The reset output stays at L level after power on. the time depends on the capacitor at pin 13.

### Manufacturer: SGS

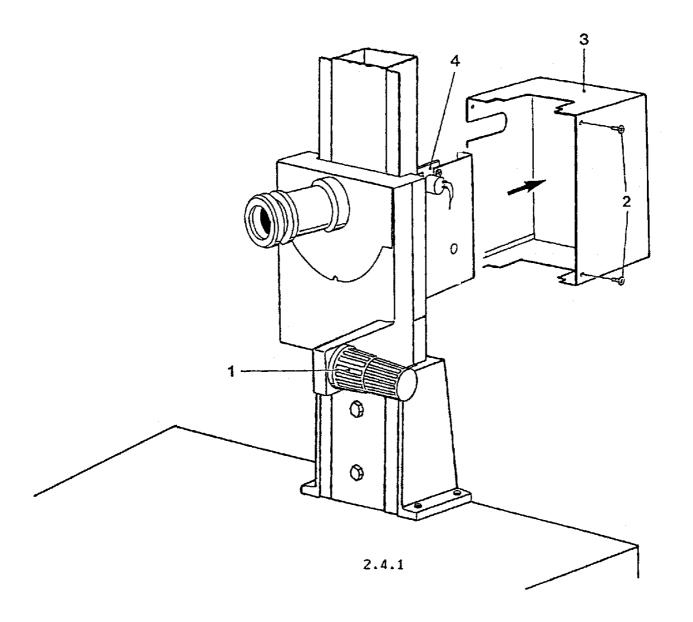

# 2.4 FACTOR POTENTIOMETER: REPLACEMENT AND CALIBRATION

### REPLACEMENT:

-----

- 1. Move head to lowest position

- 2. Block head with friction grip (1)

- 3. Remove screws (2) and cover (3)

- 4. Remove potentiometer support plate (4)

- 5. Install new pot on support plate. Turn axle clockwise to stop

- 6. Turn axle counterclockwise for 1/2 revolution

- 7. Install in reverse order

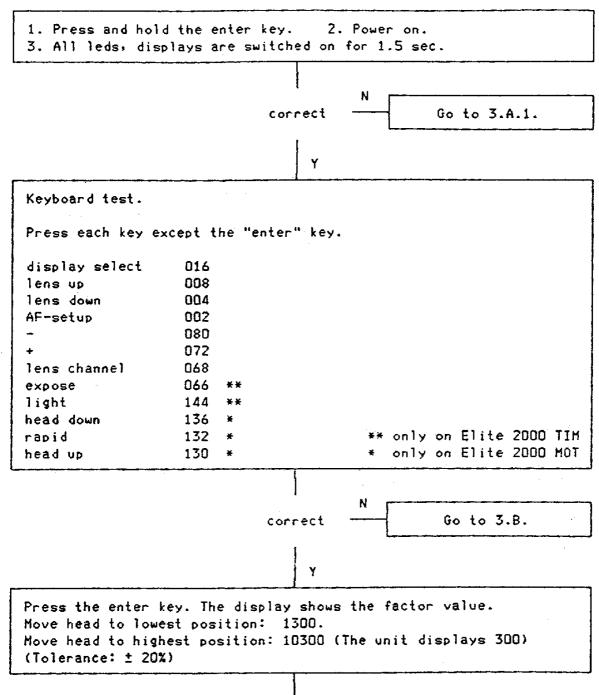

### Electronical

| Action                                                               | Purpose                                                                     |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------|

| <ol> <li>Press and hold the enter key.</li> <li>Power up.</li> </ol> | Entry into testprogram.                                                     |

| 2. Press enter.                                                      | Exit from keyboard test: The unit displays a number except 0.               |

| 3. Press the AF setup and enter keys simultaneously.                 | Entry into factor calibration procedure. The "NV" led turns on.             |

| 4. Move head to lowest position. Press enter.                        | Lowest head positon value is stored. "PV" led turns on: "NV" led turns off. |

| 5. Move head to highest position.<br>Press enter.                    | Highest head positon value is stored. The "PV" led turns off.               |

| 6. Power off to exit.                                                |                                                                             |

This procedure initializes the head limit position registers.

The potentiometer values in highest and lowest head position are stored in the ram. This obviates a precise mechanical adjustment.

### 3.2 TESTPROGRAM

#### ENTRY INTO TESTPROGRAM

### 3.3 CONTINUOUS TESTPROGRAM

#### CONTINUOUS TESTPROGRAM A:

- 1. Press enter.

- 2. Press the "up" and "down" keys simultaneously.

- 3. Lens stage moves down for 30 mm. Stops. Moves up to ref. position.

#### CONTINUOUS TESTPROGRAM B:

- 1. Power off to exit testprogram A.

- 2. Power on with enter key pressed.

- 3. Nove head to the first focussing position of channel 0. Press "lens up" + "displ. select".

- 4. If channel 0 is programmed, and the potentiometer has been calibrated, the lens stage focusses as follows:

9 times random position 1 time focus position.

### CONTINUOUS TESTPROGRAM C: (with ELITE 2000 MOT only)

- 1. Power off to exit testprogram B.

- 2. Power on with enter key pressed.

- 3. Press the "Rapid" and "Light" keys.

The head moves to upper and lower limit.

The lens moves from reference to 100 mm extension and back.

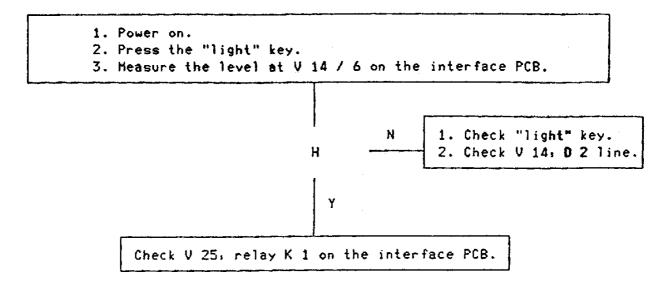

### 3.A FLOWCHART

The unit is completely dark

—— Y —— Use 3.C.1 chart.

The unit enters the operating mode

--- Y --- Go to 3.B.

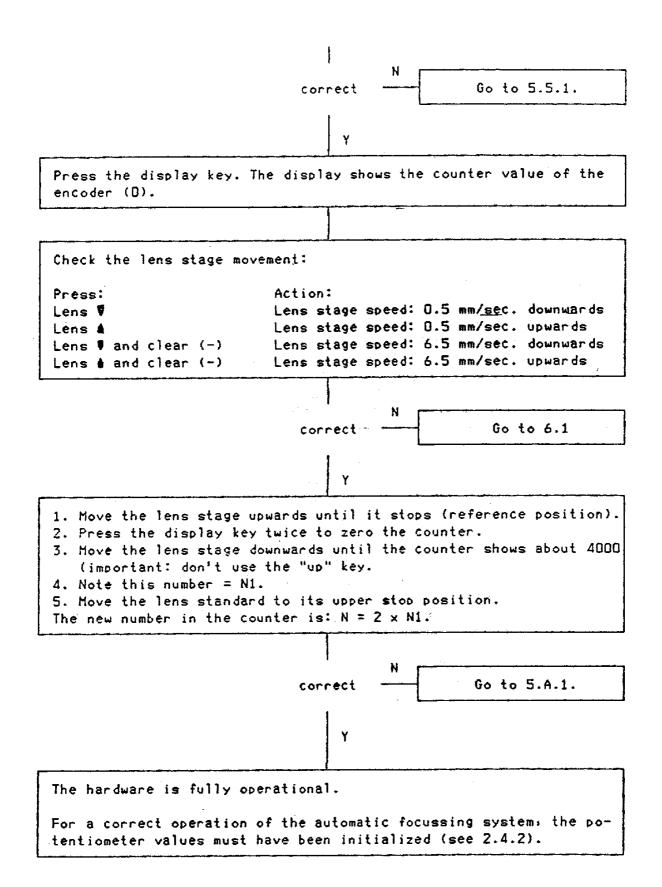

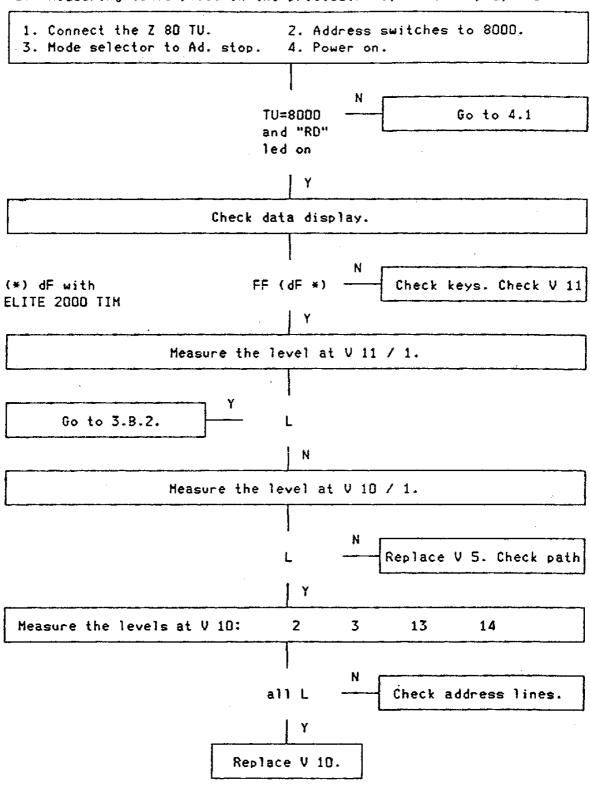

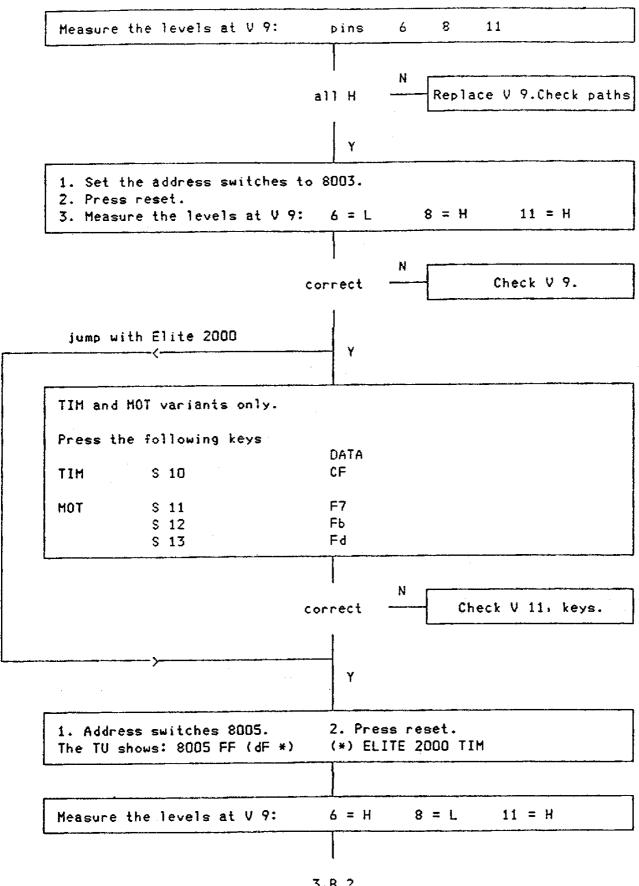

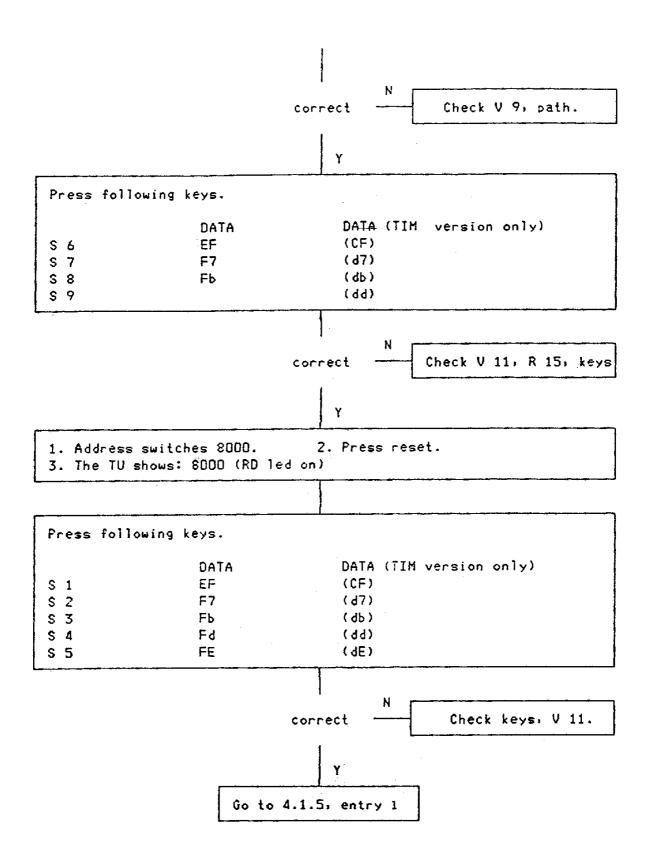

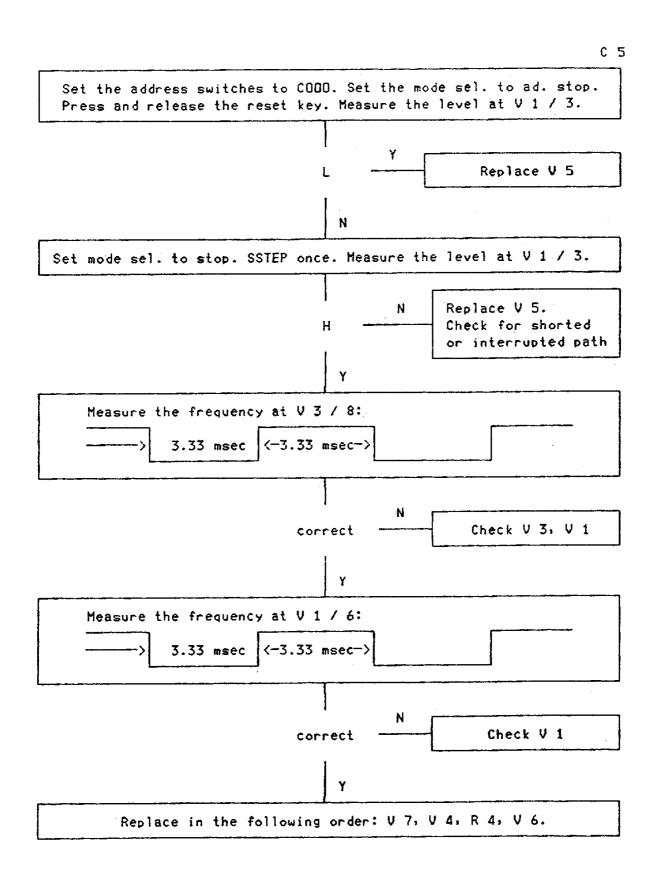

## 3.B FLOWCHART: Processor keyboard display PCB

(all measuring takes place on the processor keyboard display PCB)

3.B.1

3.B.2

3.B.3

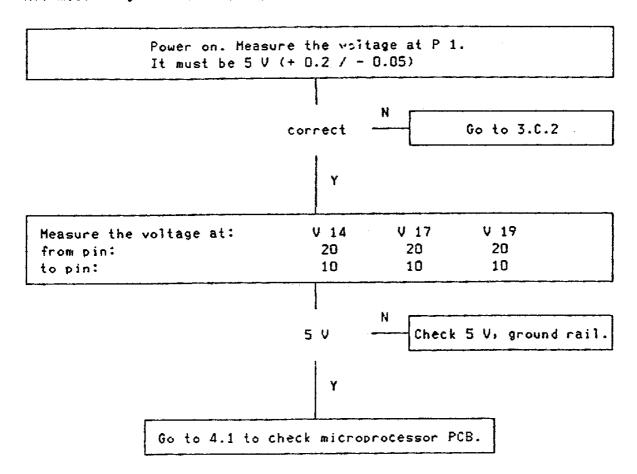

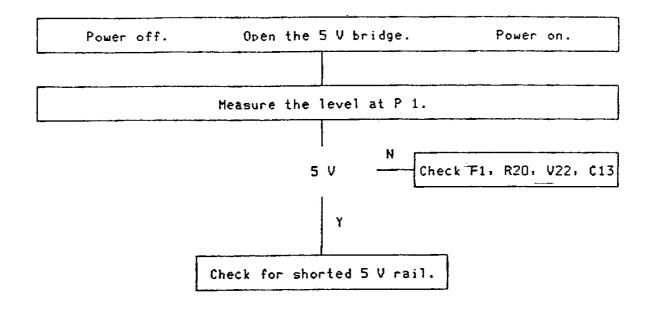

# 3.C FLOWCHART: Power supply

All measuring refers to PCB power control.

END

END

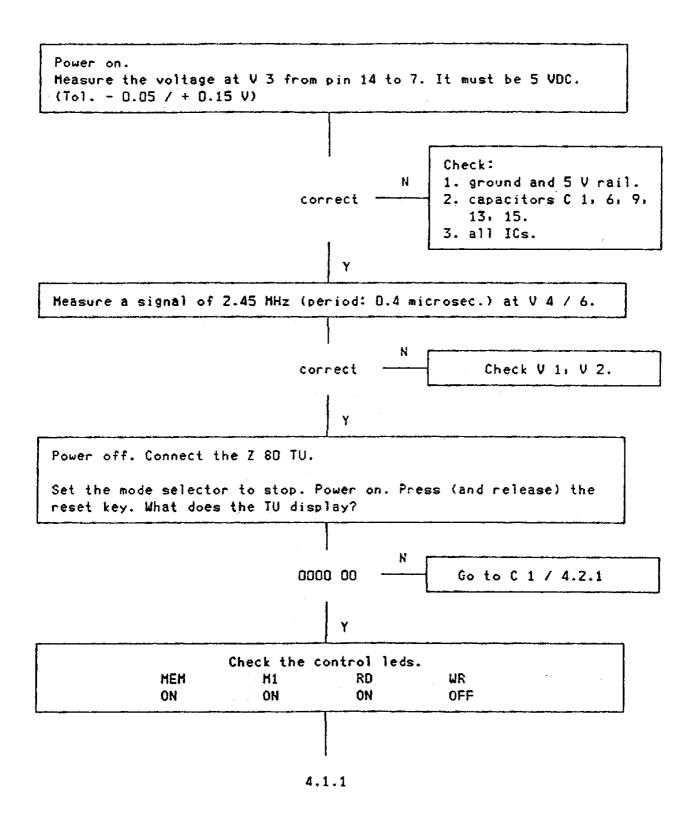

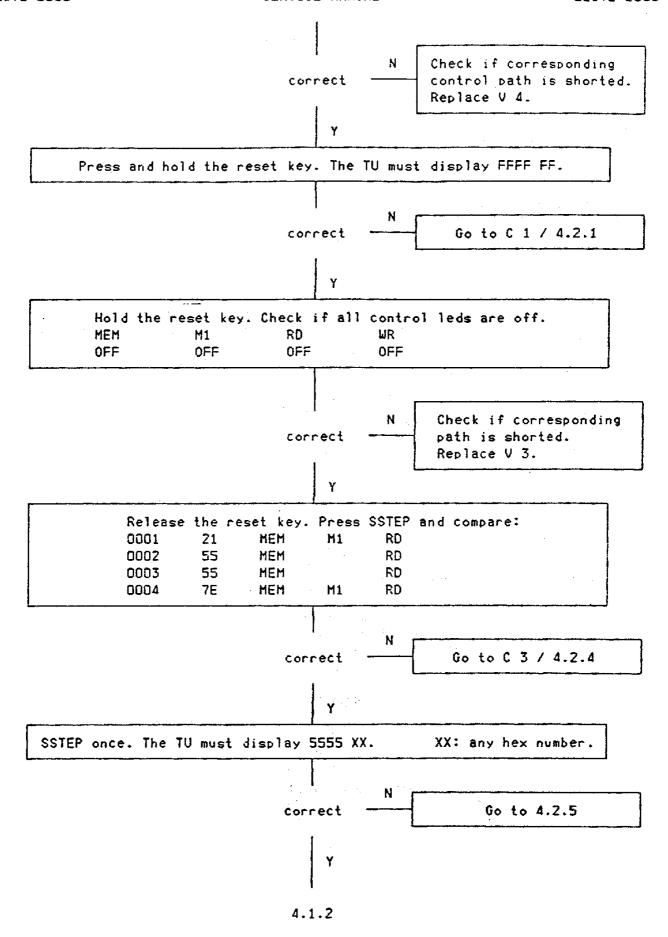

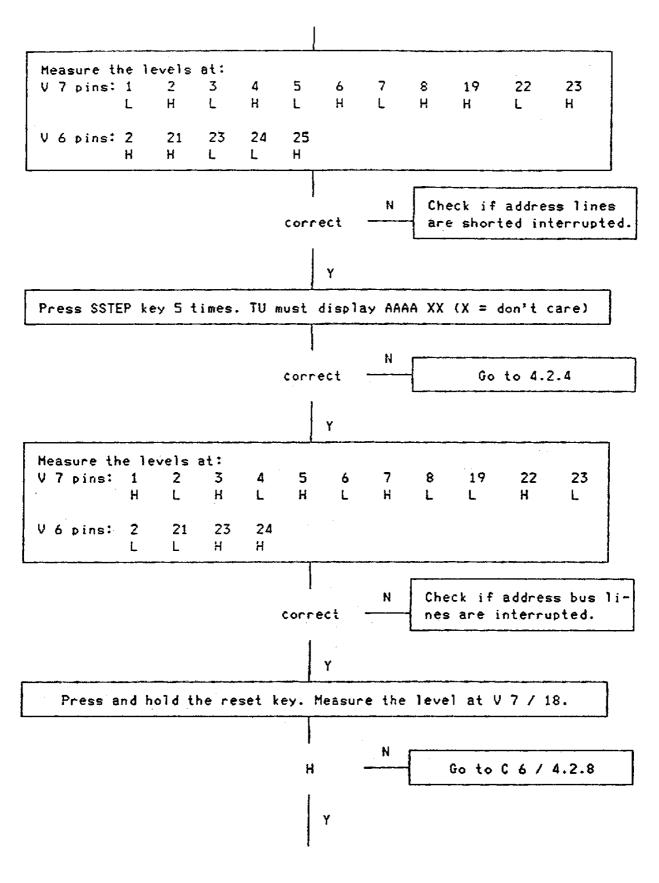

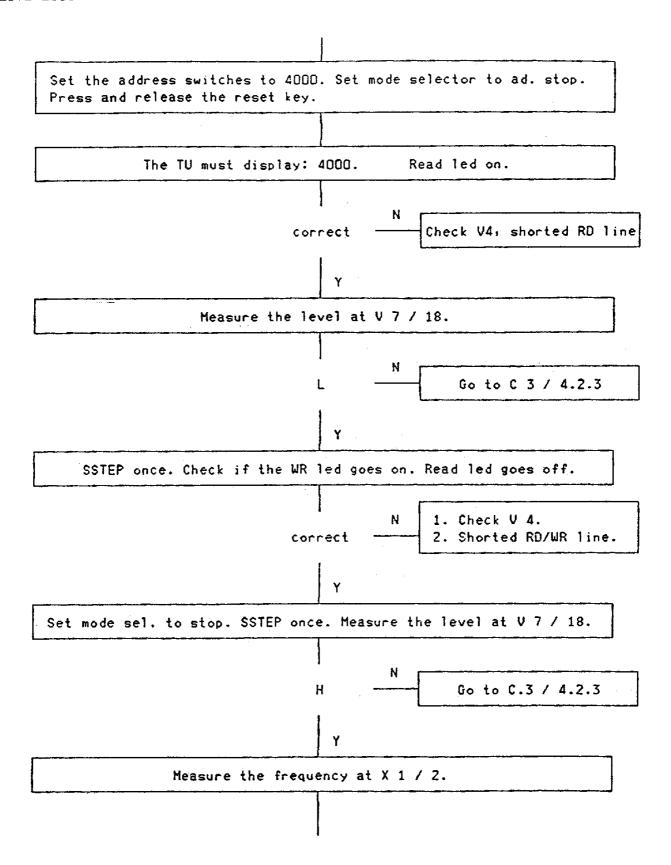

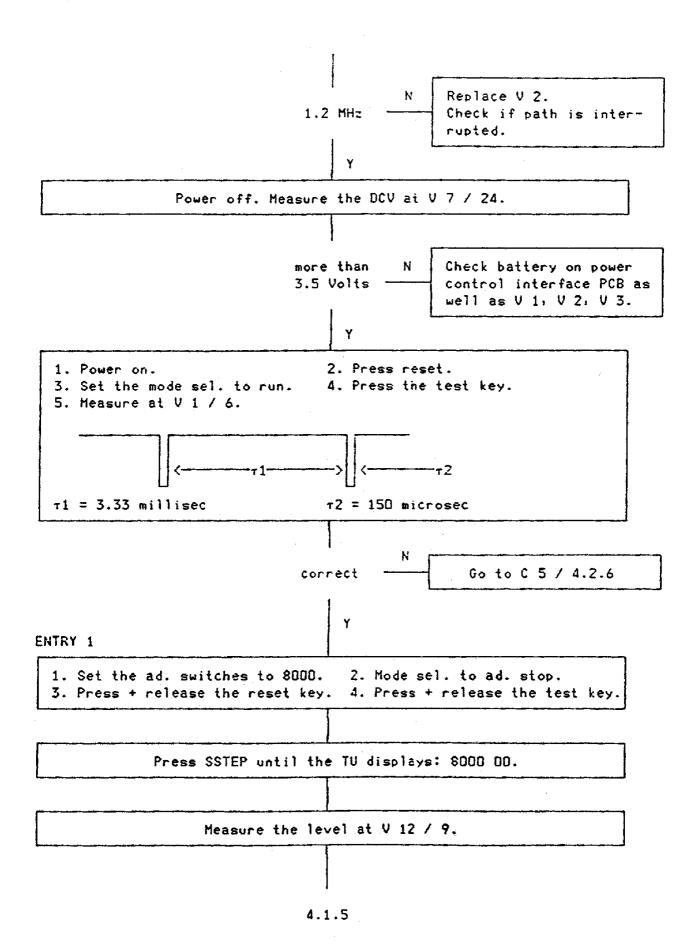

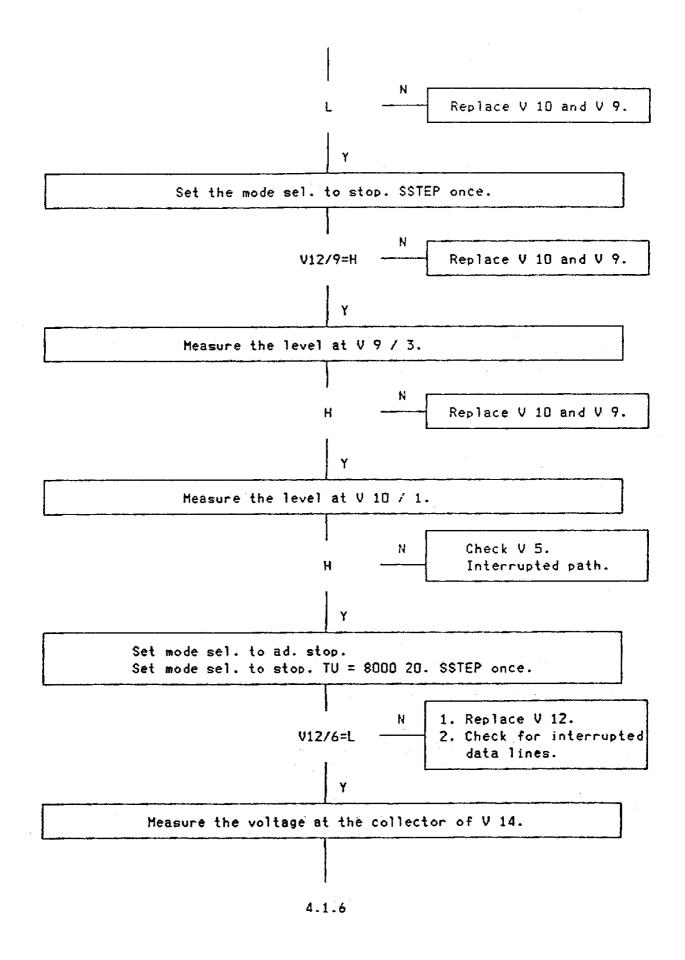

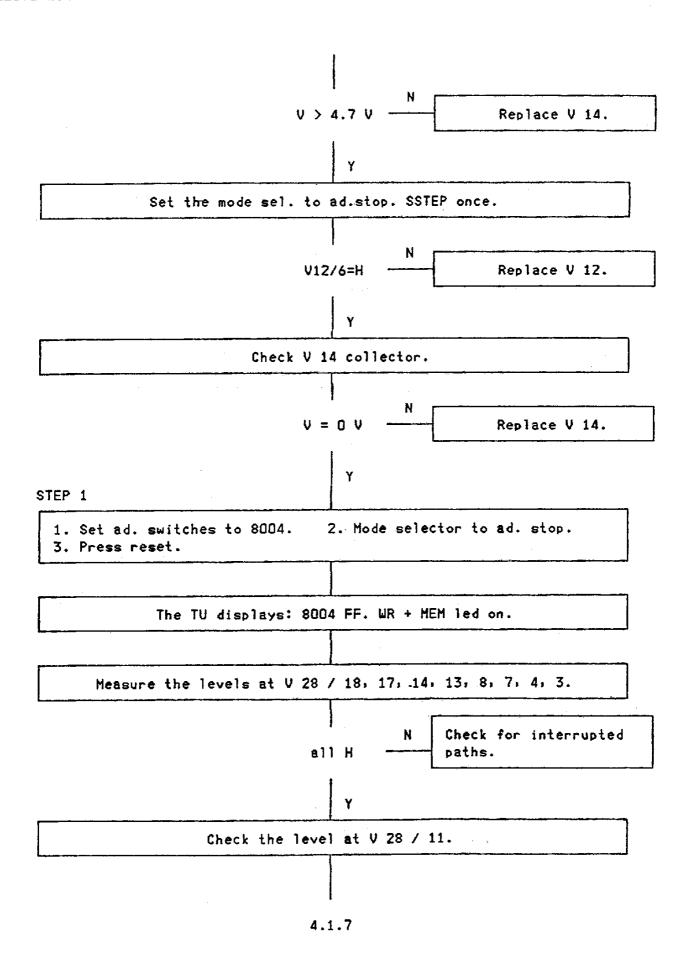

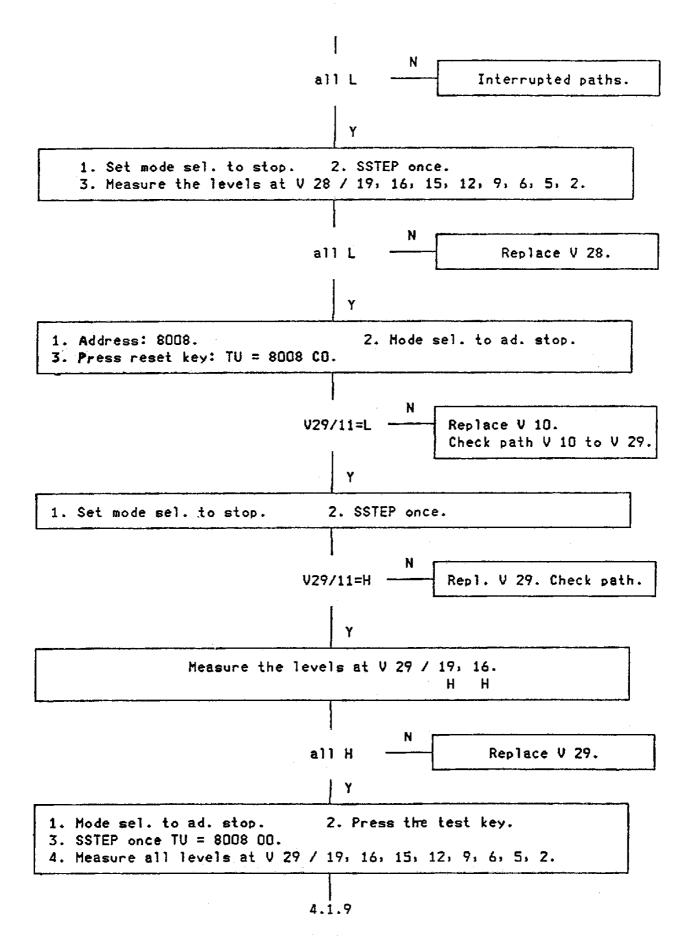

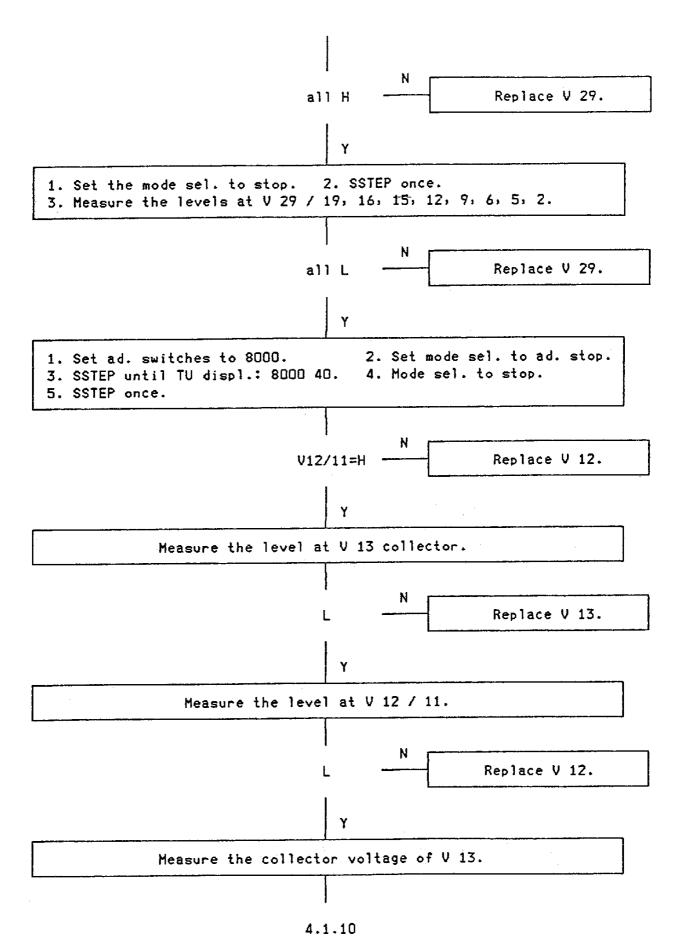

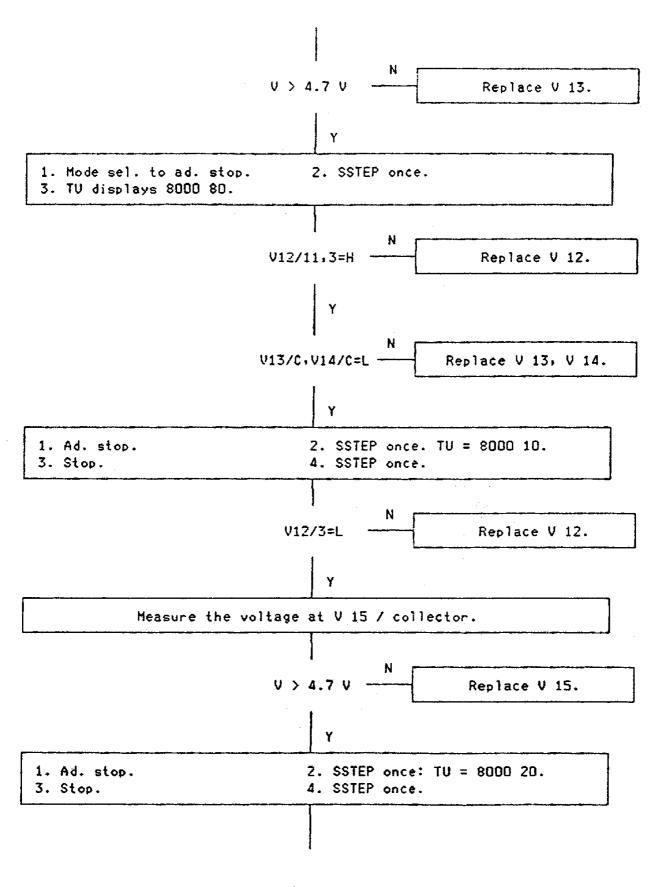

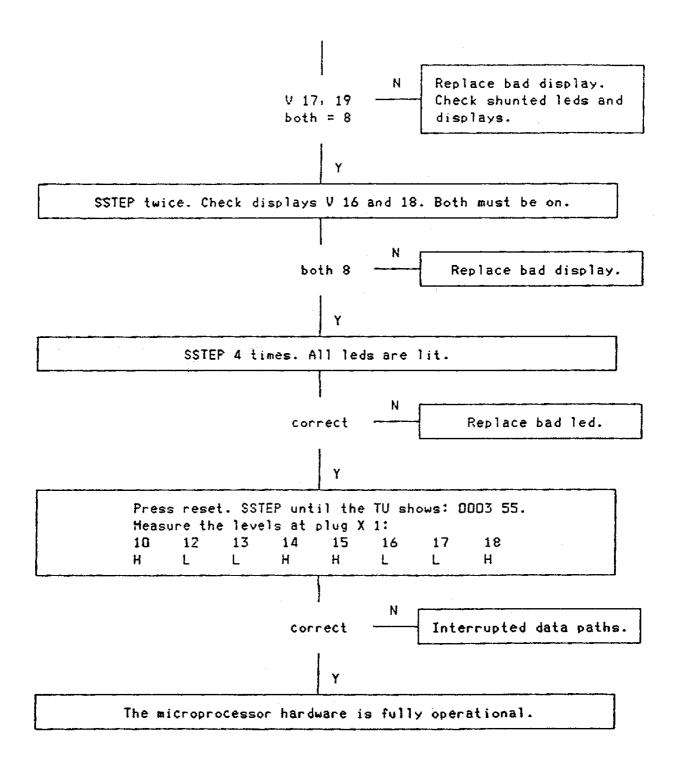

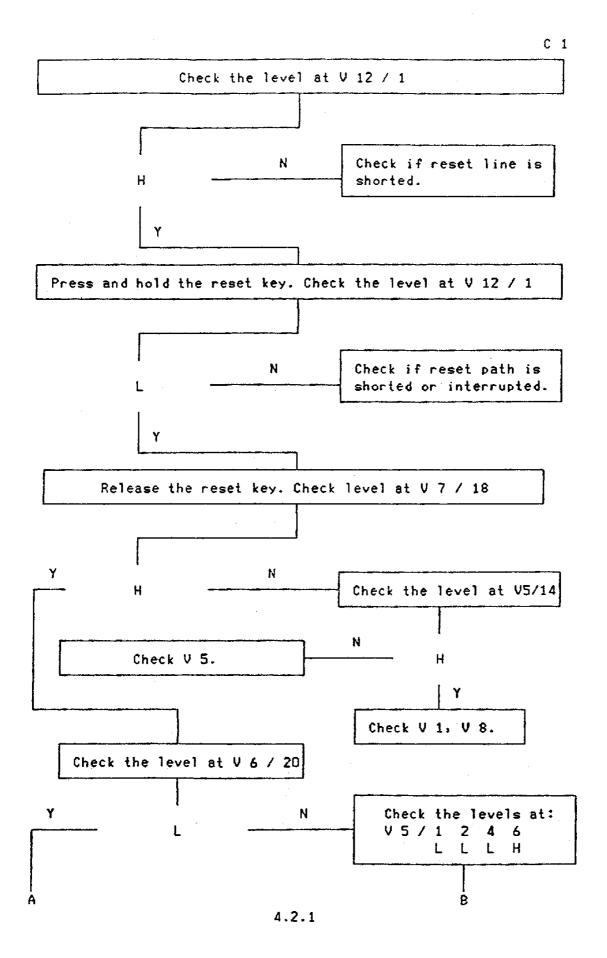

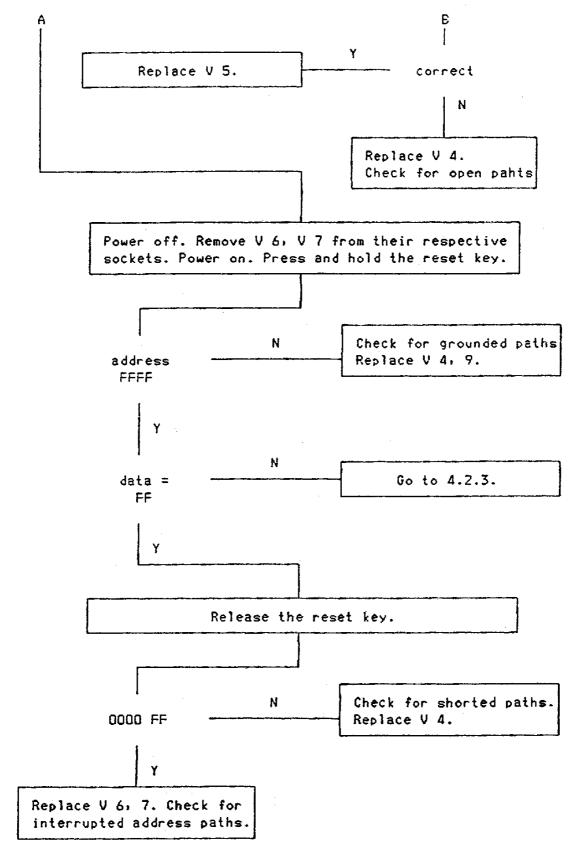

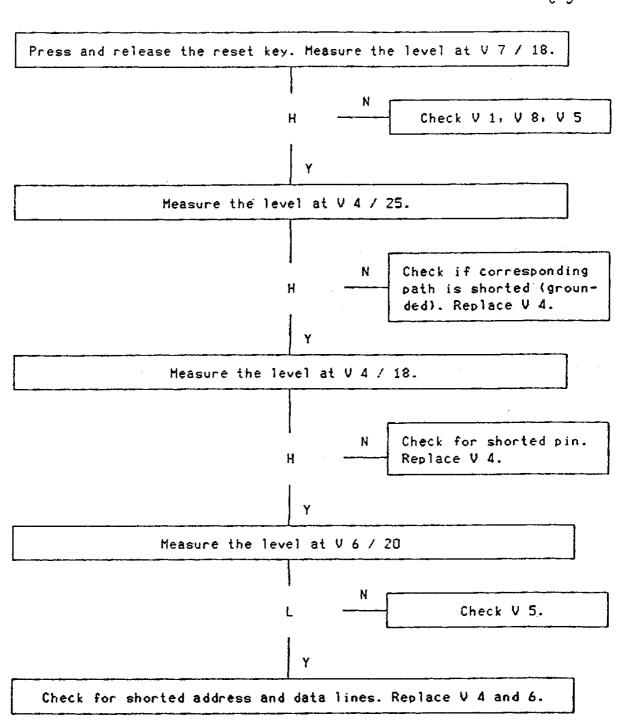

### 4.1 PROCESSOR PCB

#### Note:

All ICs mentioned throughout this section are located on the microprocessor board: MA60345

4.1.3

4.1.11

4.2.2

C 3

STEP 1

C 4

Shorted address / data lines.

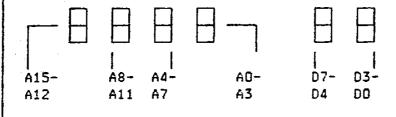

Each digit in the TU displays the state of four address and data lines respectively. As the Z 80 has 16 address and 8 data lines, the TU needs 4 digits to read the address bus and 2 digits to read the data bus. Each half-byte-(4 bits) is represented in an hexadecimal number. Consequently the first digit on the TU, starting left, shows the logic states of address lines A 15 - A 12, the second one shows them from A 8 to A 11 and so on.

C 6

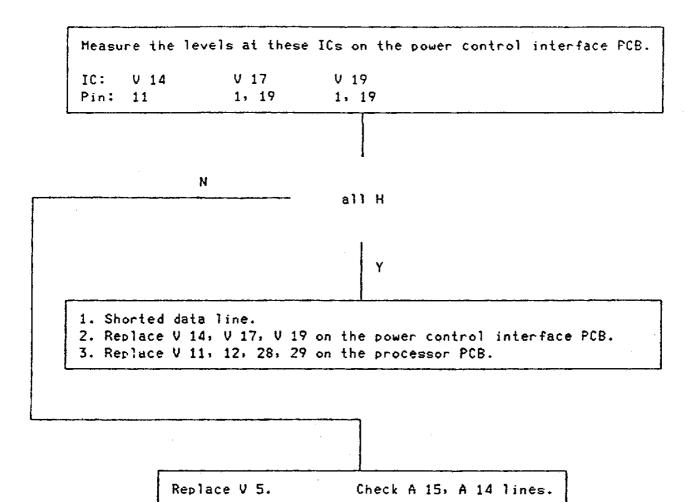

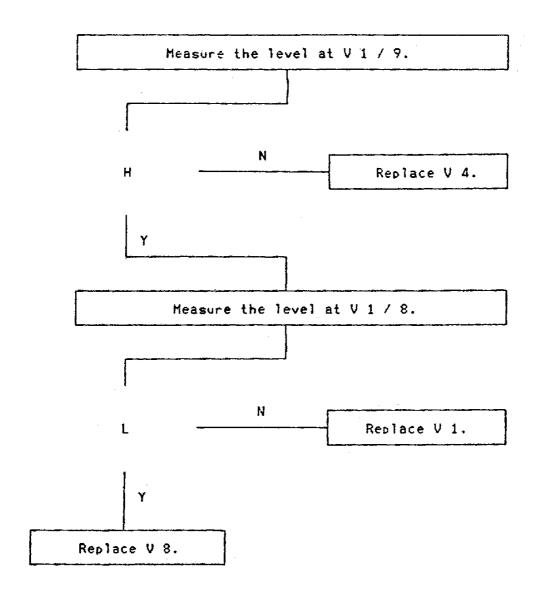

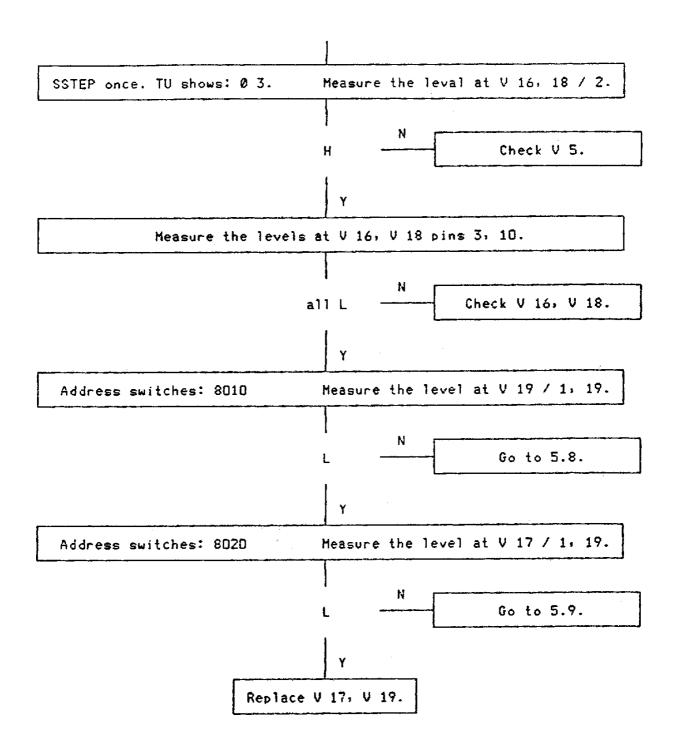

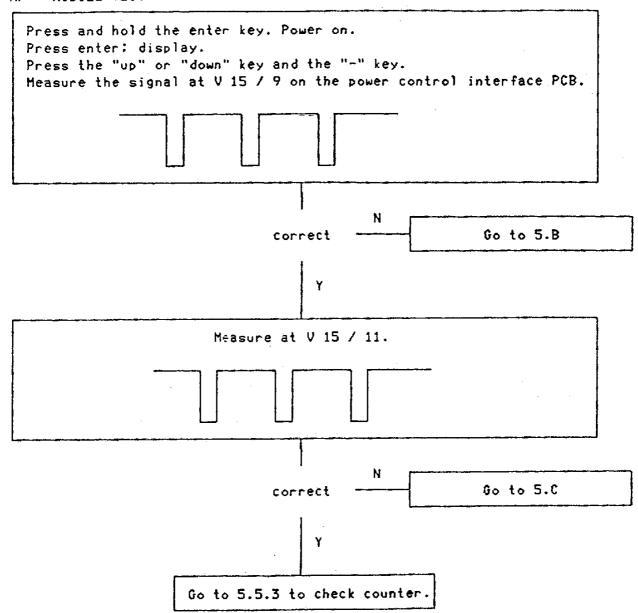

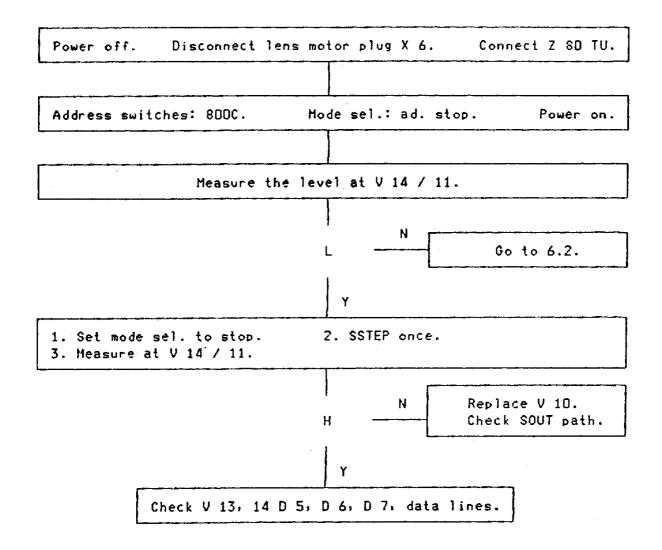

## 5.5 INTERFACE PCB

### FAILURE CHART 5.6

All measuring takes place on the power control PCB.

All measuring takes place on the power control PCB.

Measure the level at V 14 / 11.

N Replace V 10, 9, 5 on the processor PCB.

Y

Set mode sel. to stop. SSTEP once. Measure at V 14 / 11.

N Replace V 10 (processor PCB).

Check sout path.

Y

Replace V 14. Check paths. Check V 6, V 5.

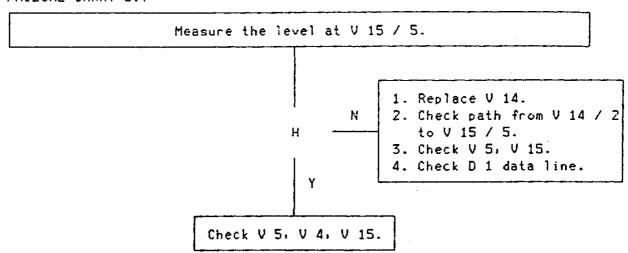

#### FAILURE CHART 5.7

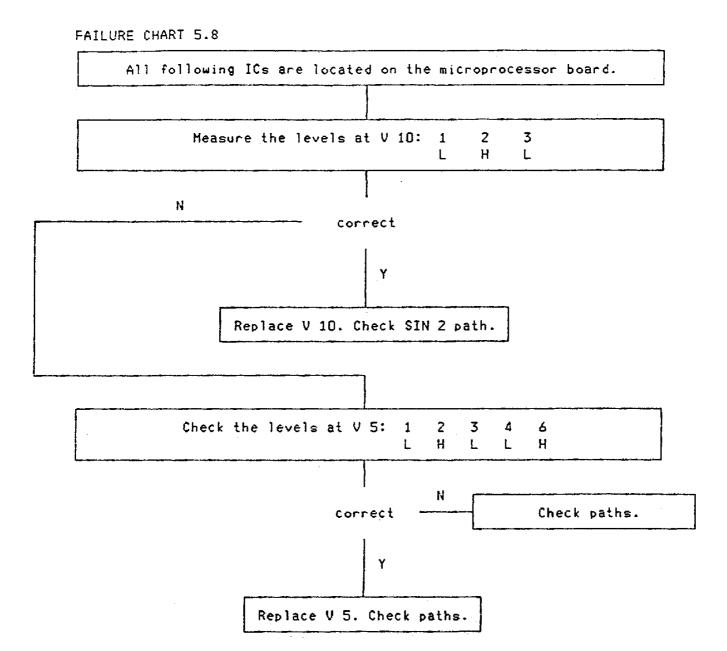

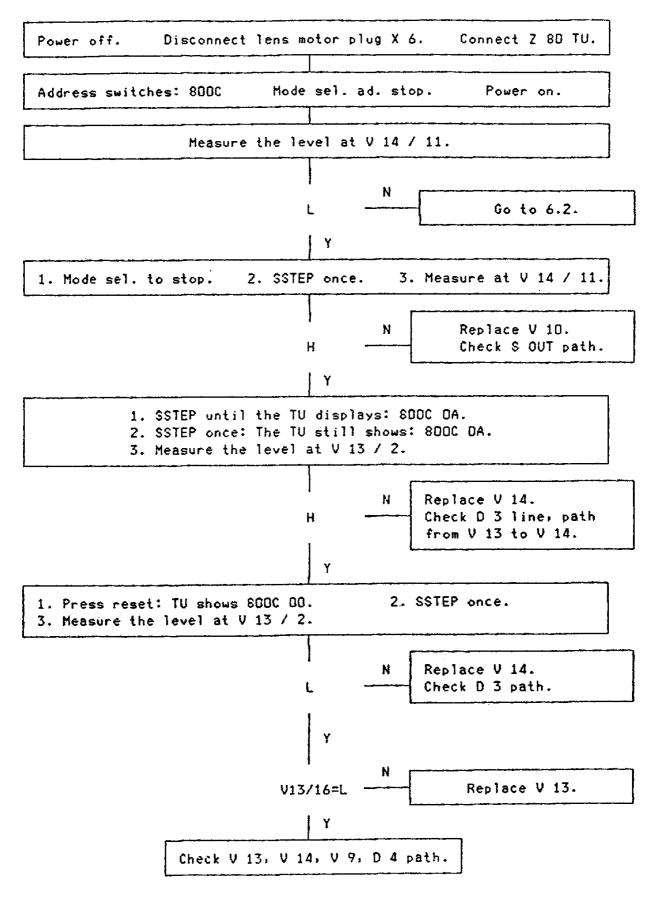

# FAILURE CHART 5.9 All following ICs are located on the microprocessor board. 2 Measure the levels at V 10: 1 3 Н N correct γ Replace V 10. Check SIN 1 path. Check the levels at V 5: 1 2 6 H L L Н correct Check paths. Replace V 5. Check paths.

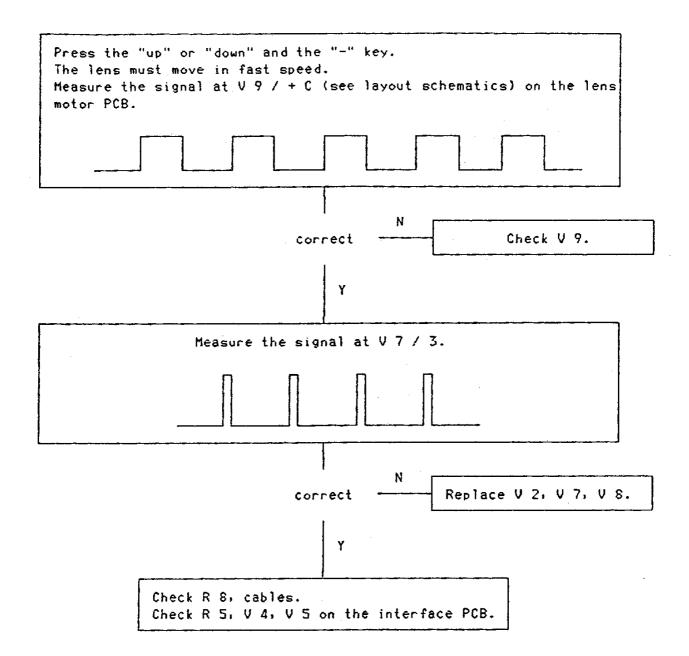

### AF - MODULE TEST

### Following failures are possible:

The speed is not accurate:

- 1. Check spindle for dirt.

- 2. The low speed is achieved by pulsing the "up" or "down" command.

In the fast speed the command stays at H level all the time. Neither the low nor the high speed are regulated and are therefore sensitive to lopsided mains voltages. To compensate change R 1 on the lens motor PCB.

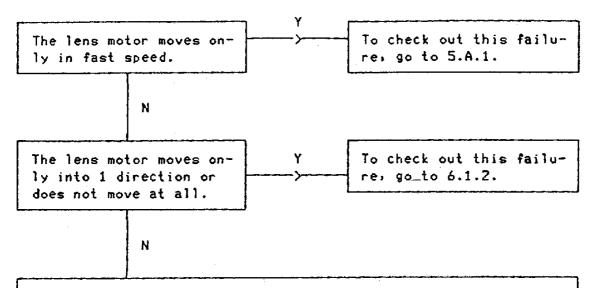

### FAILURE CHART 6.2

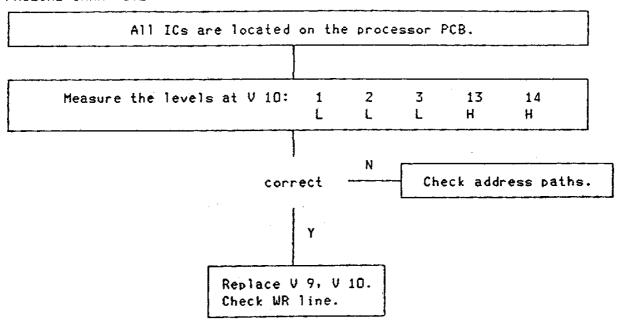

## 7.1 ELITE 2000 TIM: Lamp relay failure

LAMP RELAY CHECK (with 2000 TIM only)

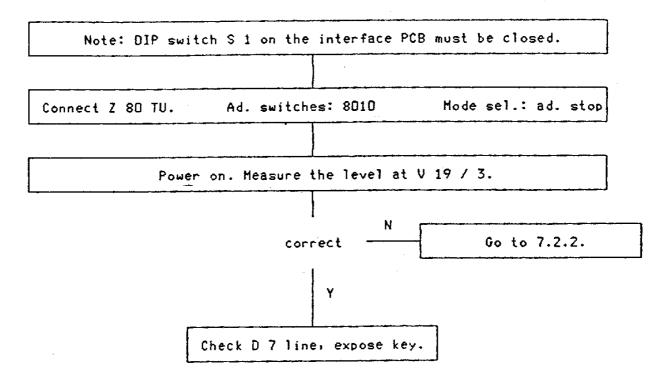

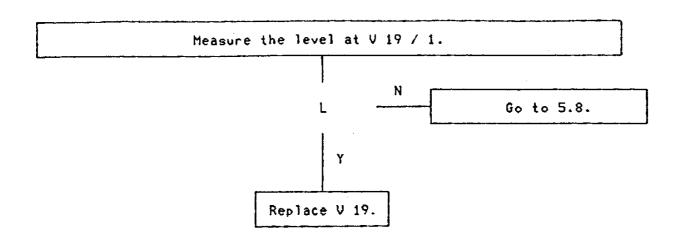

## 7.2 ELITE 2000 TIM: Timer failure

TIMER CHECK (with 2000 TIM only)

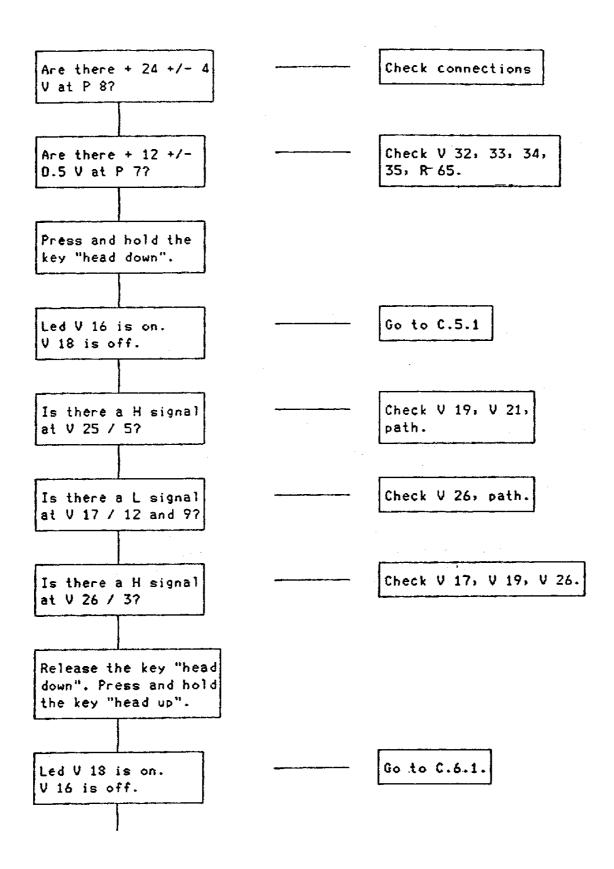

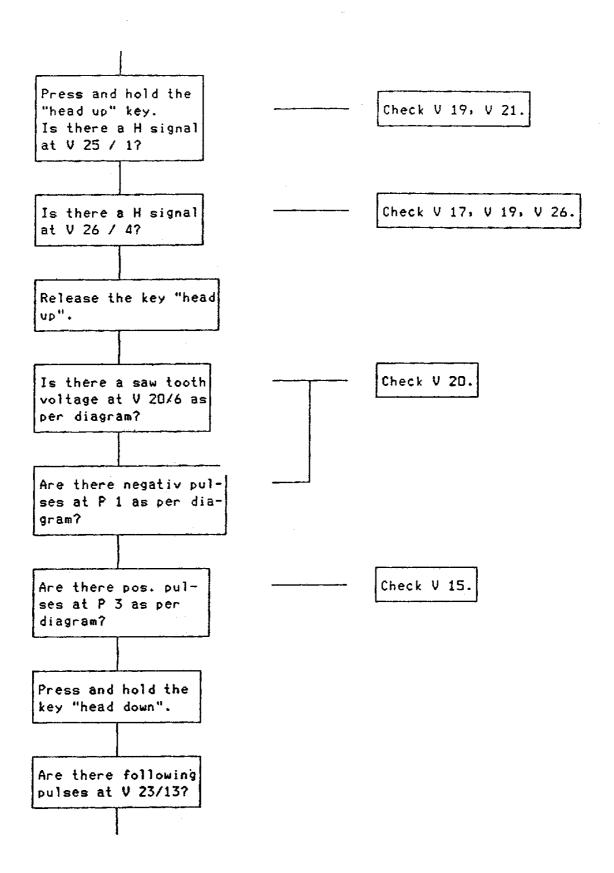

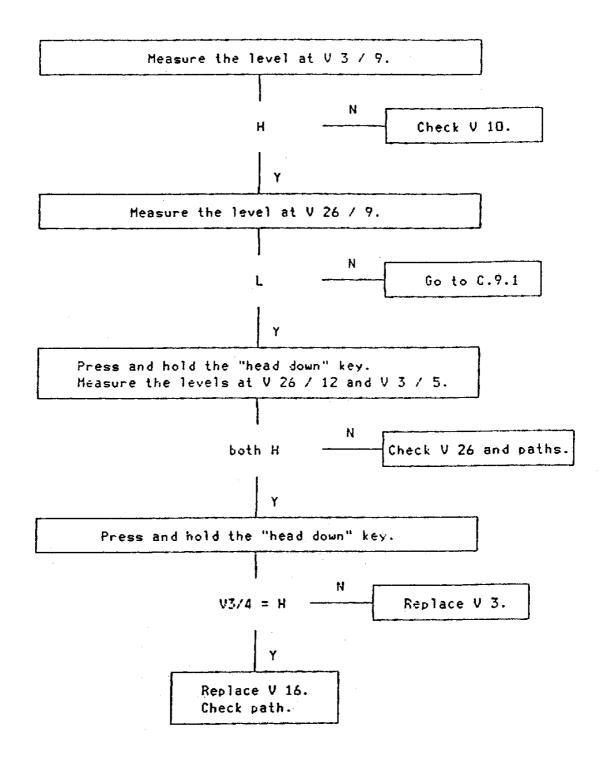

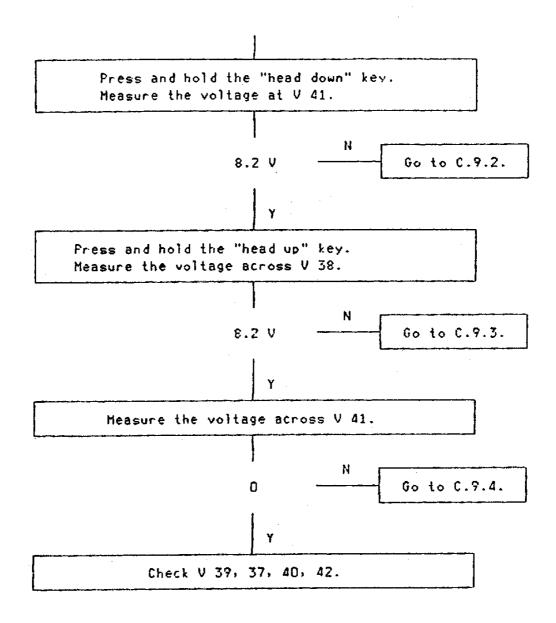

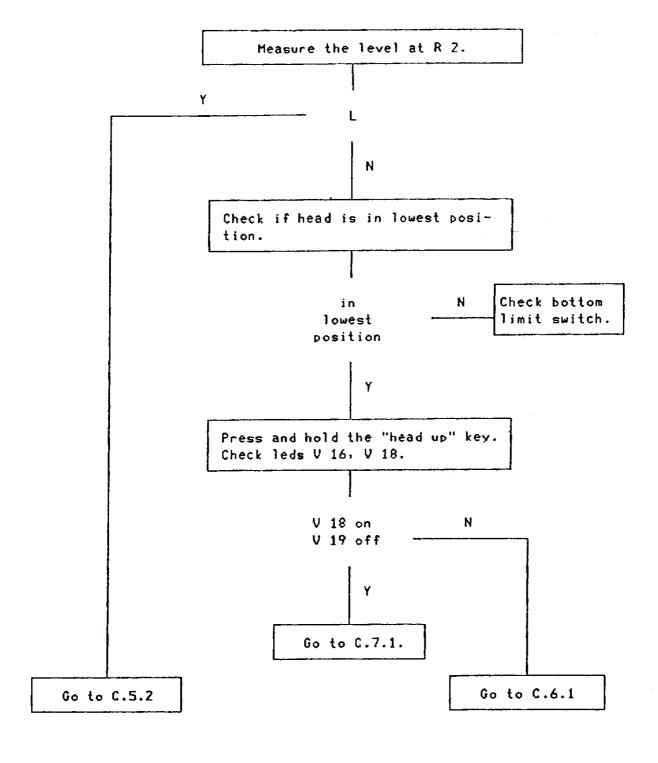

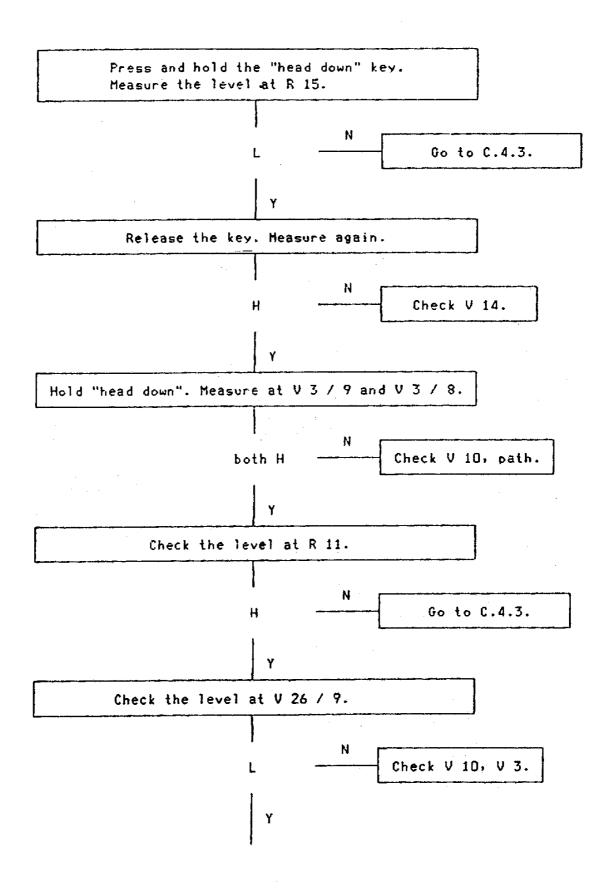

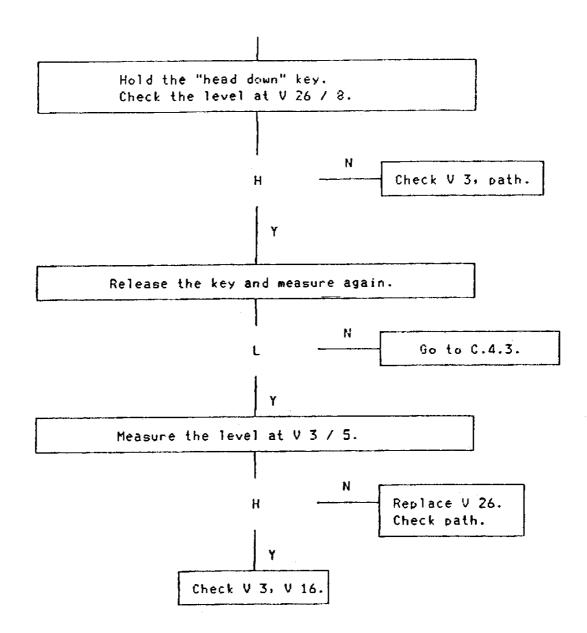

## C.O ELITE 2000 MOT: Head movement failure

| Possible faults:                                              | flowcharts |

|---------------------------------------------------------------|------------|

| The head stage cannot be moved at all                         | C.1.1      |

| The head stage can only be rai-<br>sed                        | C.2.1      |

| The head stage can only be lo-<br>wered                       | C.7.1      |

| The head moves only with high speed (or low speed is not cor- |            |

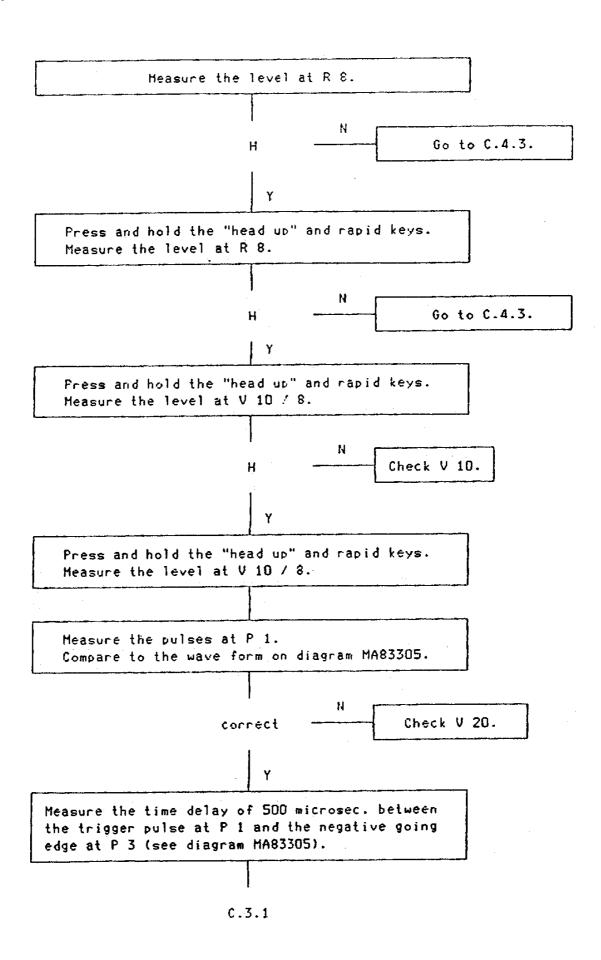

| rect and cannot be adjusted)                                  | C.3.1      |

| The head moves only with low speed                            | C.3.1      |

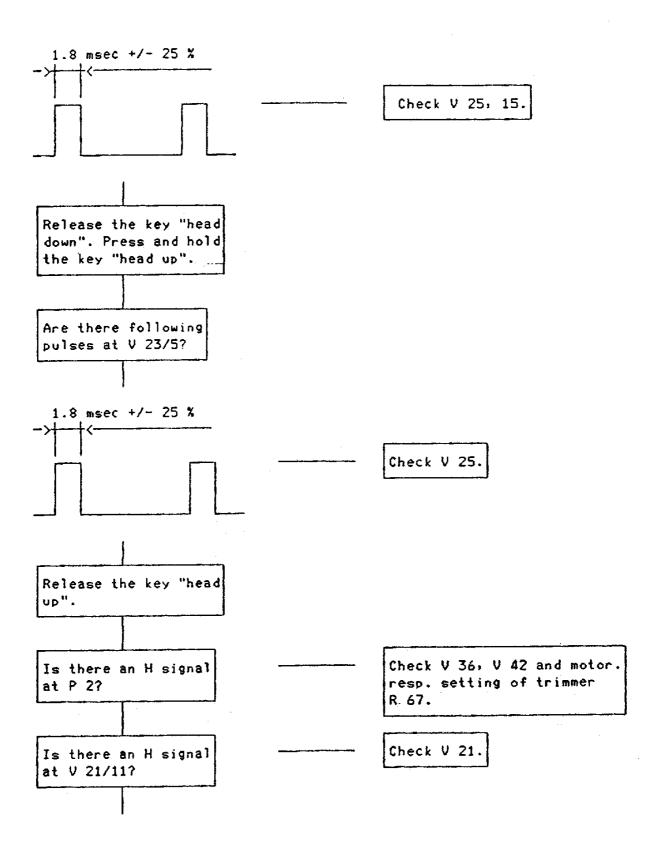

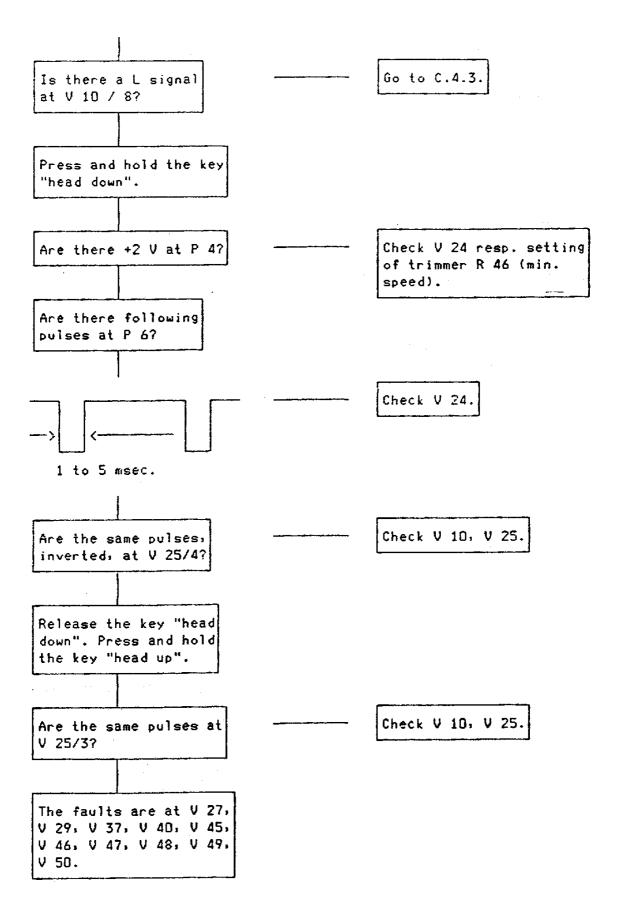

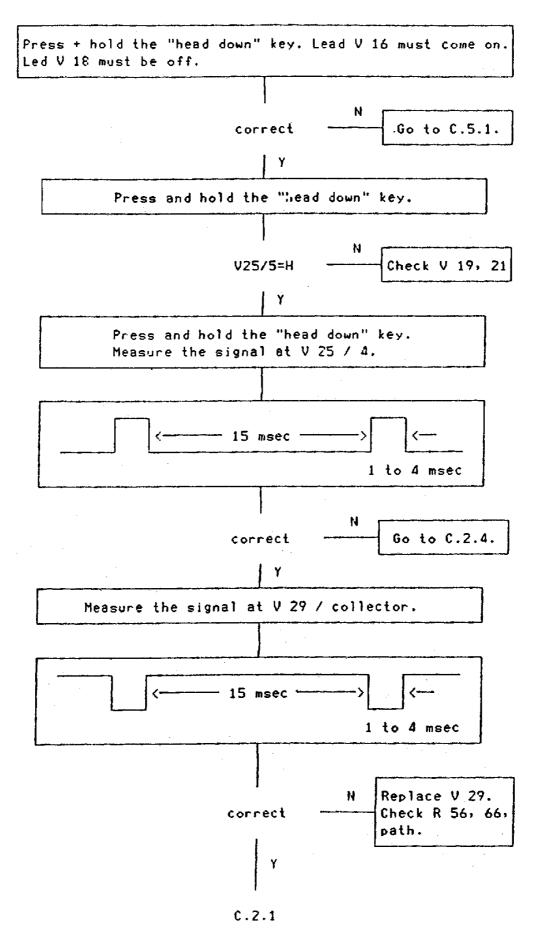

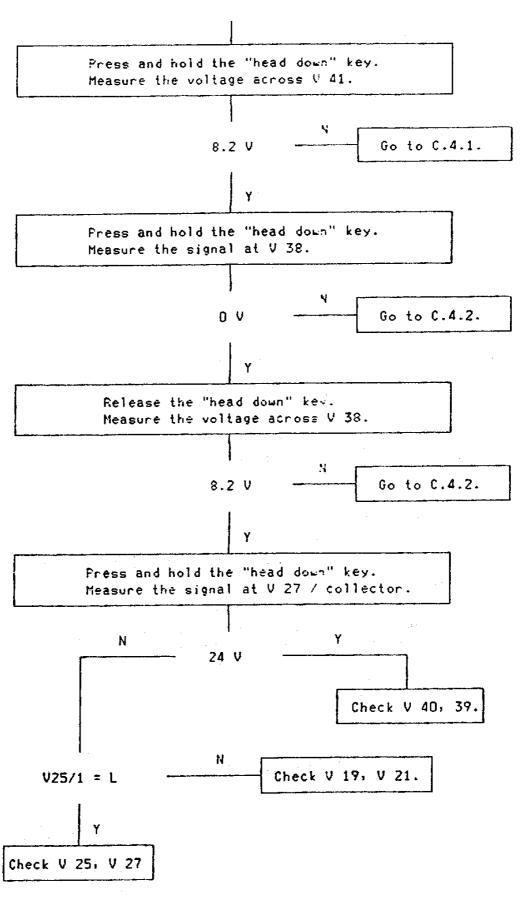

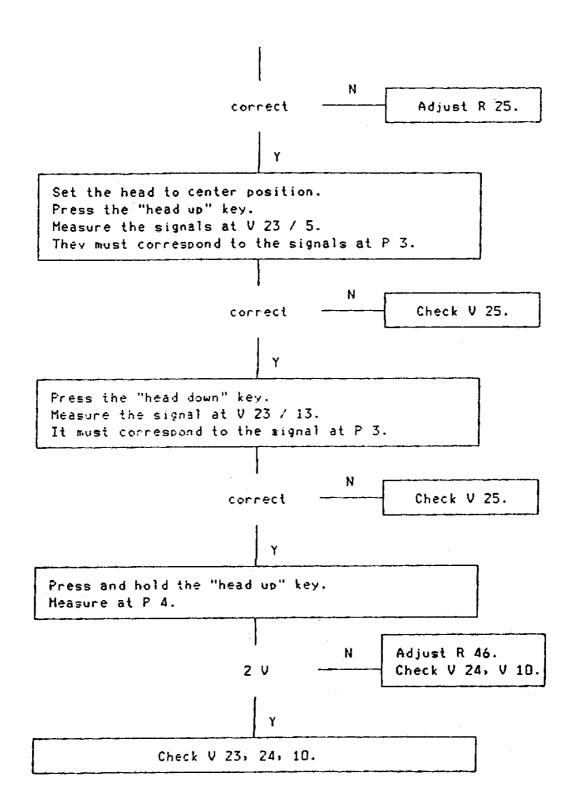

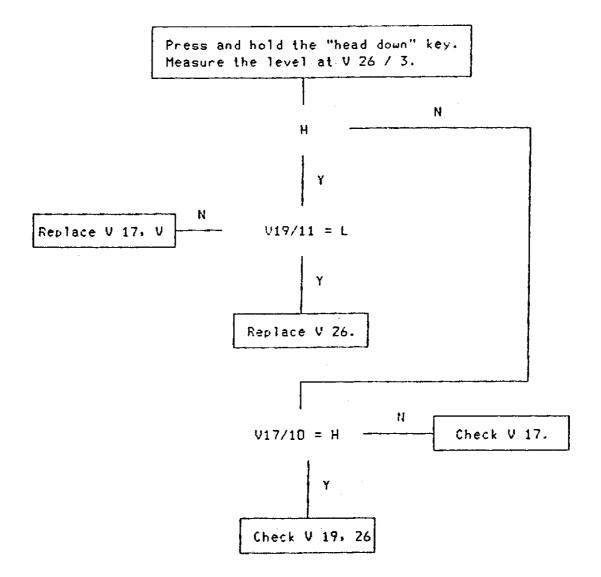

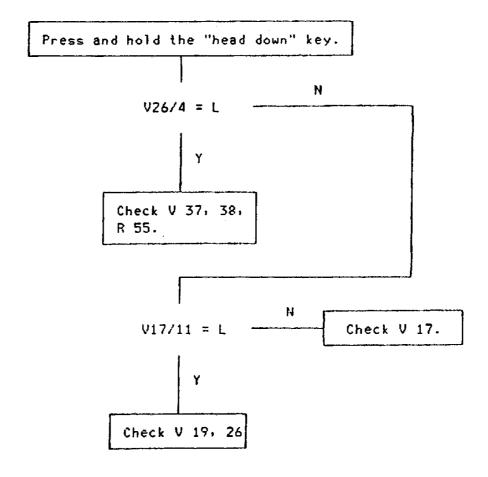

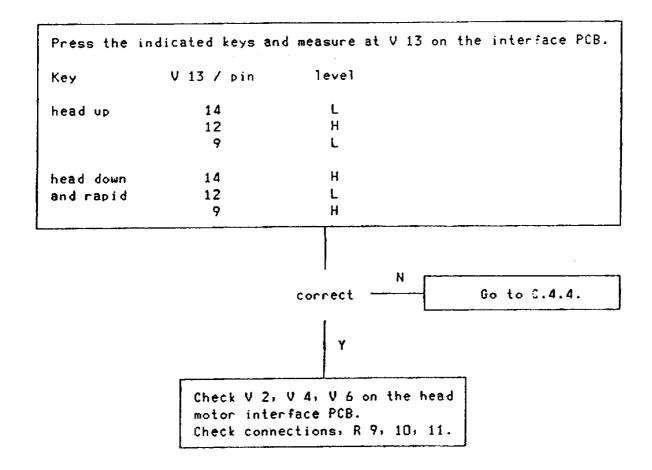

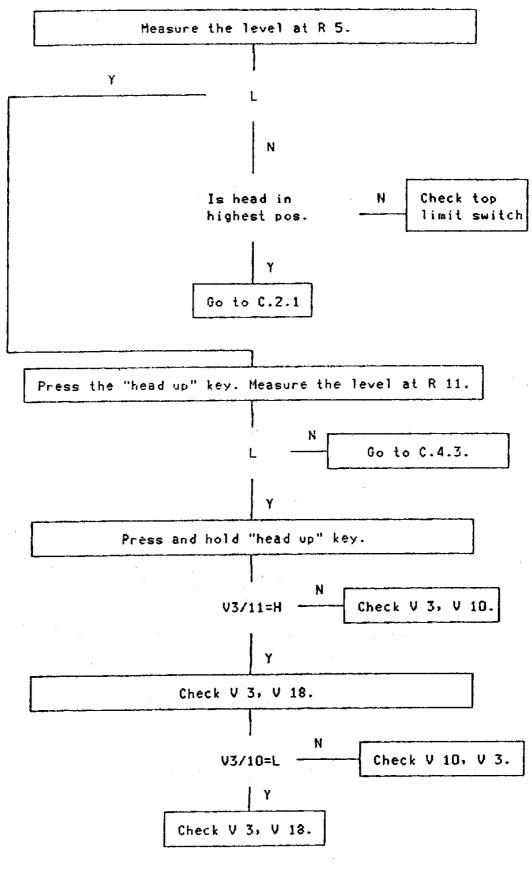

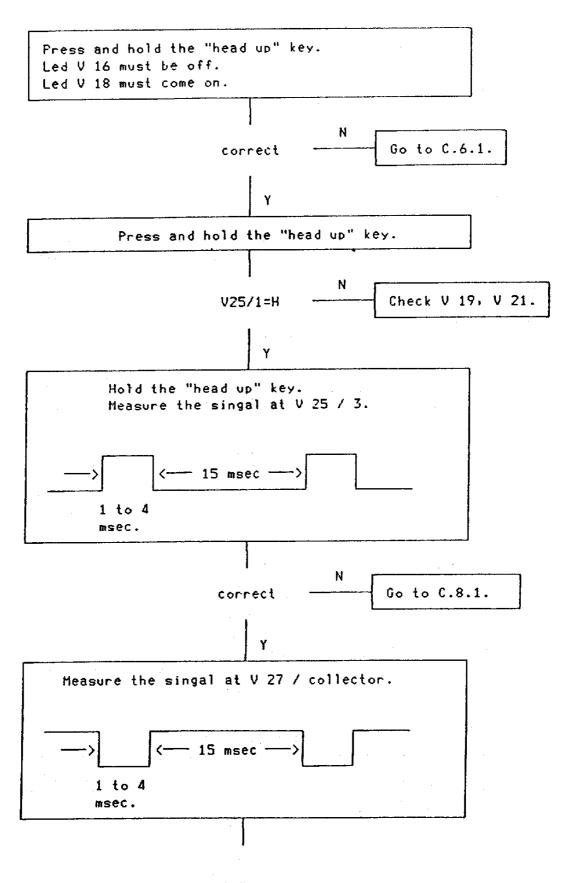

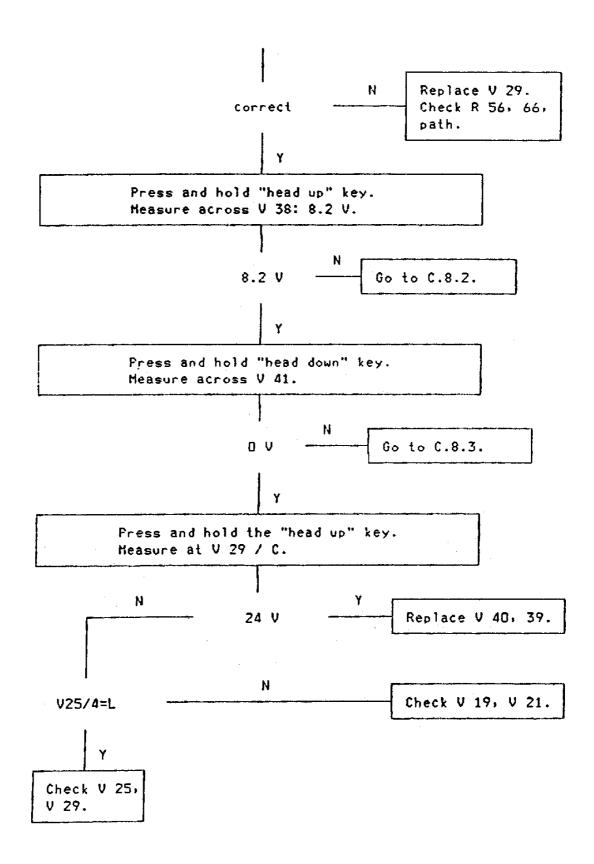

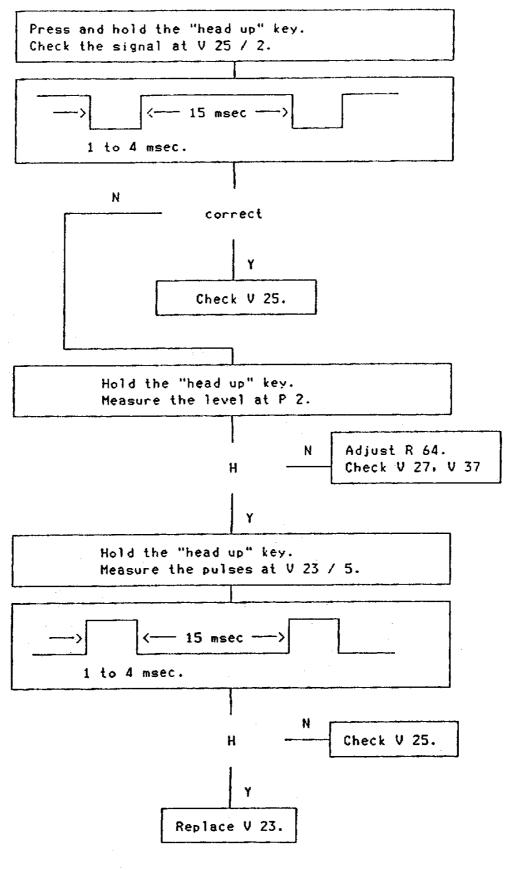

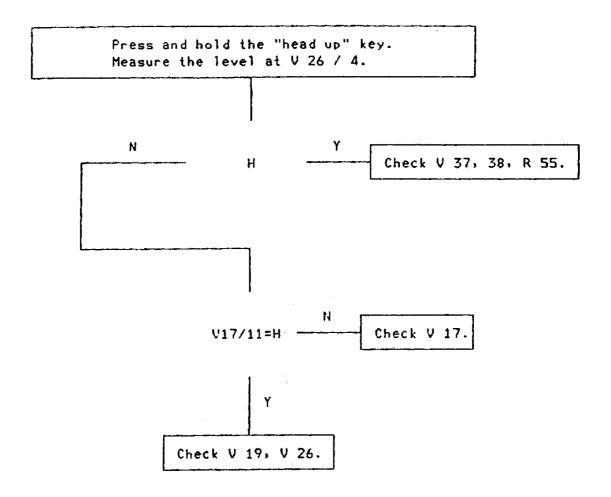

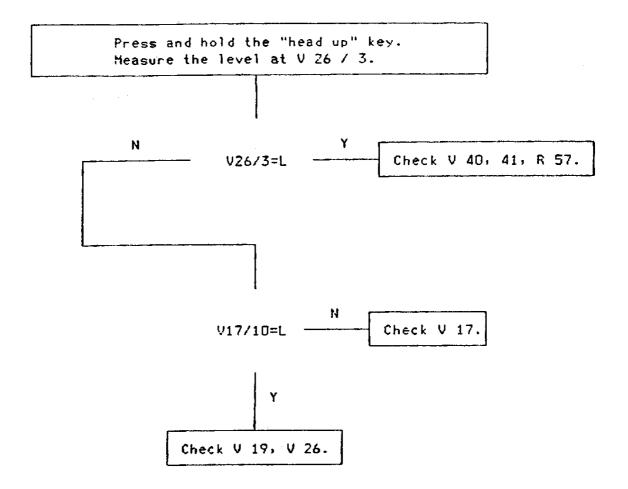

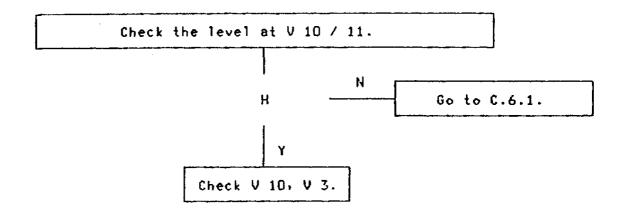

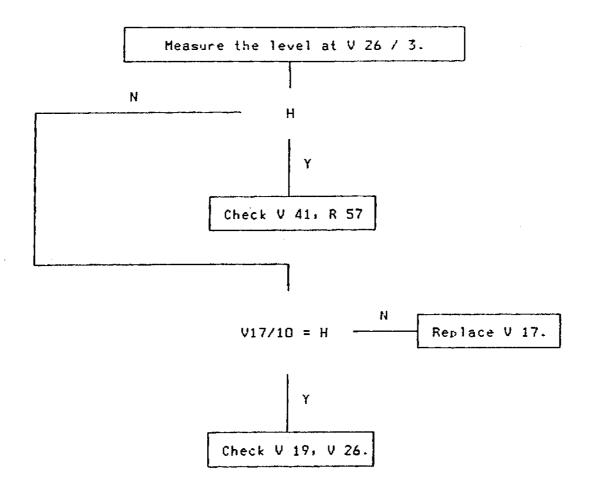

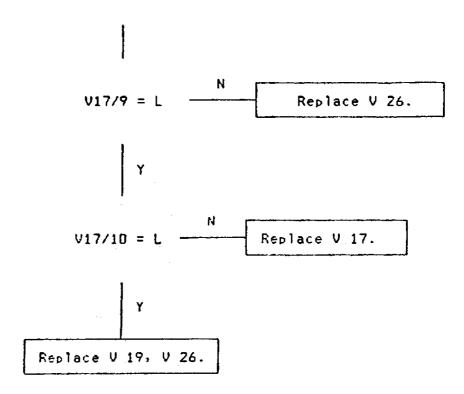

### EAILURE\_CHART

C.5.2

C.6.1

€.7.1

C.8.1

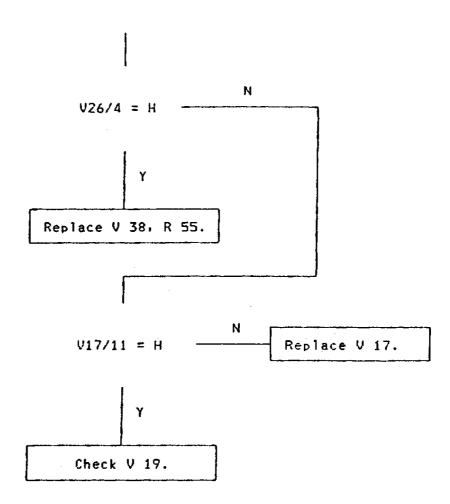

## D.1 MOTOR CONTROL 24 VOLT PCB: FUNCTIONAL DESCRIPTION

# DECODING STAGE

It consists of V 3, 10, 26.

The commands UP, DOWN and FAST are low active.

The inputs LIMIT SWITCH UP, DOWN are H active. The limit switches are closed when the head is not in the end position.

Thus, in the inactive state the limit switches connect these inputs to ground.

The and-gates V 3/c and d decode the inputs.

| DOWN<br>V 10/13 | UP<br>V 10/11 | LIMIT SW. UP<br>V 10/3 | LIMIT SW. DOWN<br>V 10/5 | V 3/10 | V 3/11 |

|-----------------|---------------|------------------------|--------------------------|--------|--------|

| L               | Н             | L                      | L                        | Н      | L      |

| H               | L             | į L                    | L                        | Ł      | l H    |

| Н               | X .           | H                      | L                        | L      | L L    |

| X               | Н             | L                      | Н                        | L      | L      |

| X               | L             | Ļ                      | Н                        | L      | н      |

| L               | X             | н                      | Ł                        | Н      | L      |

V 26/c is an EX-OR gate.

If both the up and down commands are active, output pin 10 goes to L level and stops the commands.

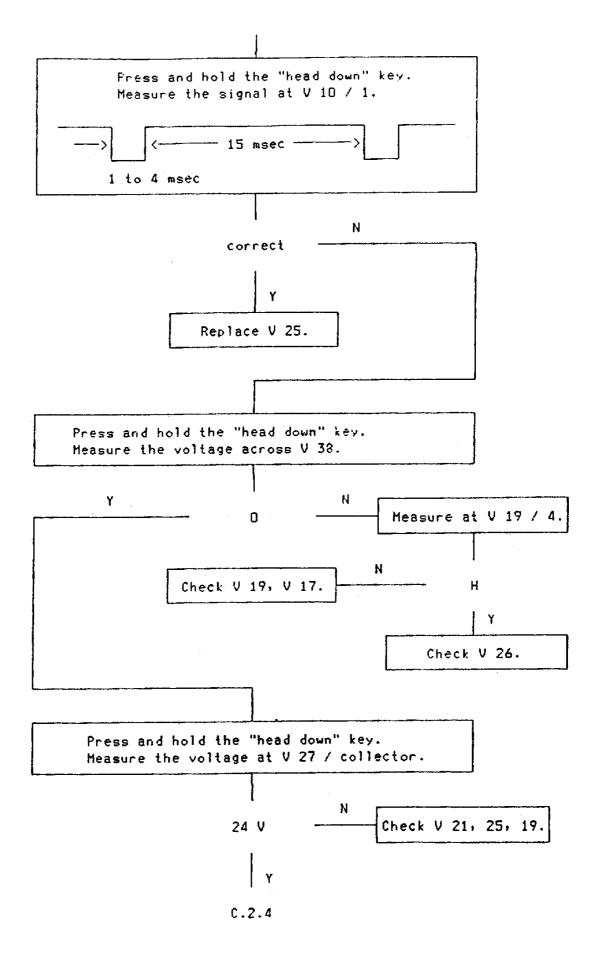

## PULSE GENERATOR

Astable mulitvibrator V 20 produces pulses (pin 3) and a sawtooth (pin 6).

The sawtooth is compared to the feedback voltage available at V 24/1 via V 24/d.

The duty-cycle at V 10/2 is proportional to the feedback voltage.

Depending on the selected function (up or down), either V 25/3 or V 25/4 follows this frequency and switches transistor V 29 (V 27).

A larger load means a higher voltage at V 24/1 and a longer duty cycle at V 10/2.

In case the "fast" key is pressed, the pulses are suppressed via V 10/d and replaced by a steady H level. Thereby the motor receives full power instead of a pulsed signal.

V 24/c is a time delay circuit, to avoid a sudden voltage increase at the motor inputs.

#### LOAD FEEDBACK

In slow speed, the load condition is measured and translated into a proportional pulse to the power drivers.

Across R 53 (down) ar R 49 (up) the driving pulses are available.

Their amplitude decreases in case the motor load increases: as the voltage drop across R 68, 69 increases as well and less voltage reaches the motor.

The pulses charge C 19 via digital switches V 23/a (up) or V 23/b (down).

Capacitor C 19 charges up to a voltage proportional to the pulse amplitude.

At pin 7 of buffer V 24/b the same voltage appears.

V 24/a compares the desired speed (pin 3) to the feedback = actual speed.

The desired speed is adjusted via R 46.

The voltage available at V 24/1 is therefore proportional to the difference desired speed - actual speed.

Thru digital switches V 23/a, b the feedback—is syncronized to the control pulses; monostable V 15 activates these switches to this purpose.

To achieve a high efficiency slow speed regulation, the motor speed is pulsecontrolled.

The period of these pulses is sufficiently short to guarantee smooth motion.

The bridge configuration allows movement in both directions without the need of a dual supply voltage.

# OVERLOAD PROTECTION

An electronic fuse protects motor and power stage from overload and short circuit condition.

The voltage drop across R 68, 69 is proportional to the motor load.

Part of this voltage drop reaches transistor V 36. If it exceeds 0.7 volts, V 36, 37 become conductive and trigger flip-flop V 21/c, d.

Pin 13 of V 24 is forced to L level. Consequently V 10/2 stays at L level and the driving transistors are disactivated.

The motor current is interrupted.

Flip-flop V 21 is reset by astable V 20.

If the short circuit condition persists, the flip-flop V 21 is set again.

## BLOCK DIAGRAM

The property of Durst Phototechnik AG. Copying of this document, and giving it to others and the use or communication of the contents thereof, are forbidden without express authority. Offenders are liable to the payment of damages. All rights are reserved in the event of the grant of a patent or the registration of a utility model or design.

# durst

Durst Phototechnik AG Division Phototechnik Postfach 223 Vittorio-Veneto-Straße 59 I-39042 Brixen, Italy Telefon 0472/83 06 20 Telefax 0472/83 09 80

e-mail: durst@durst.it

e-mail service department: <a href="mailto:service@durst.it">service@durst.it</a>

Internet: <a href="mailto:www.durst-online.com/">www.durst.it</a>